Interrupt processing, Interrupt latency, Atar862-8 – Rainbow Electronics ATAR862-8 User Manual

Page 19

19

ATAR862-8

4589B–4BMCU–02/03

Interrupt Processing

For processing the eight interrupt levels, the MARC4 includes an interrupt controller with

two 8-bit wide interrupt pending and interrupt active registers. The interrupt controller

samples all interrupt requests during every non-I/O instruction cycle and latches these in

the interrupt pending register. If no higher priority interrupt is present in the interrupt

active register, it signals the CPU to interrupt the current program execution. If the inter-

rupt enable bit is set, the processor enters an interrupt acknowledge cycle. During this

cycle a short call (SCALL) instruction to the service routine is executed and the current

PC is saved on the return stack. An interrupt service routine is completed with the RTI

instruction. This instruction resets the corresponding bits in the interrupt pending/active

register and fetches the return address from the return stack to the program counter.

When the interrupt enable flag is reset (triggering of interrupt routines is disabled), the

execution of new interrupt service routines is inhibited but not the logging of the interrupt

requests in the interrupt pending register. The execution of the interrupt is delayed until

the interrupt enable flag is set again. Note that interrupts are only lost if an interrupt

request occurs while the corresponding bit in the pending register is still set (i.e., the

interrupt service routine is not yet finished).

It should be noted that automatic stacking of the RBR is not carried out by the hardware

and so if ROM banking is used, the RBR must be stacked on the expression stack by

the application program and restored before the RTI. After a master reset (power-on,

brown-out or watchdog reset), the interrupt enable flag and the interrupt pending and

interrupt active register are all reset.

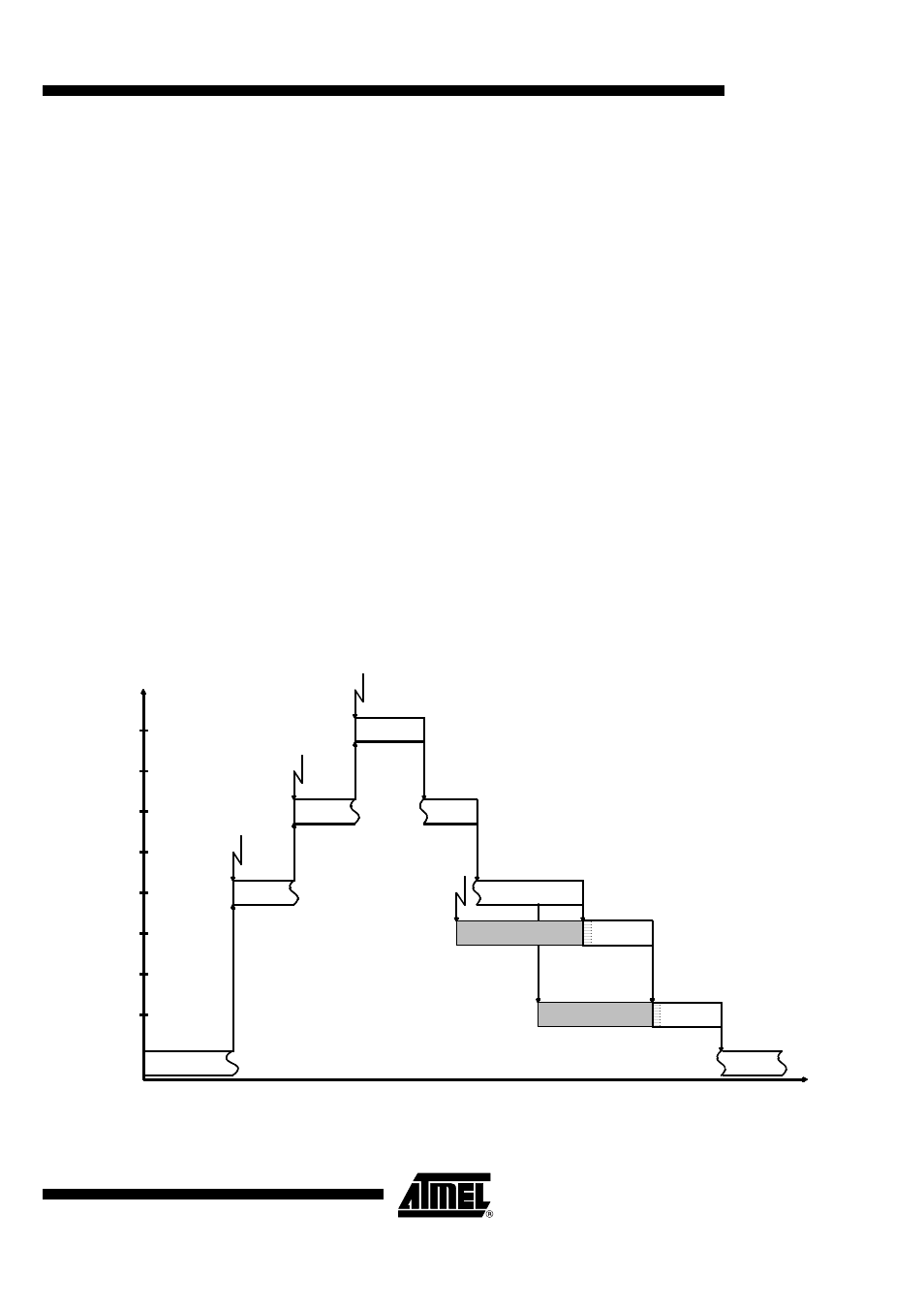

Interrupt Latency

The interrupt latency is the time from the occurrence of the interrupt to the interrupt ser-

vice routine being activated. This is extremely short (taking between 3 to 5 machine

cycles depending on the state of the core).

Figure 15.

Interrupt Handling

7

6

5

4

3

2

1

0

Pr

ior

ity level

INT5 active

INT7 active

INT2 pending

SWI0

INT2 active

INT0 pending

INT0 active

INT2

RTI

RTI

INT5

INT3 active

INT3

RTI

RTI

RTI

INT7

Time

Main /

Autosleep

Main /

Autosleep