Mcl bus protocol, Atar862-8 – Rainbow Electronics ATAR862-8 User Manual

Page 72

72

ATAR862-8

4589B–4BMCU–02/03

MCL Bus Protocol

The MCL protocol constitutes a simple 2-wire bi-directional communication highway via

which devices can communicate control and data information. Although the MCL proto-

col can support multi-master bus configurations, the SSI in MCL mode is intended for

use purely as a master controller on a single master bus system. So all reference to

multiple bus control and bus contention will be omitted at this point.

All data is packaged into 8-bit telegrams plus a trailing handshaking or acknowledge-bit.

Normally the communication channel is opened with a so-called start condition, which

initializes all devices connected to the bus. This is then followed by a data telegram,

transmitted by the master controller device. This telegram usually contains an 8-bit

address code to activate a single slave device connected onto the MCL bus. Each slave

receives this address and compares it with its own unique address. The addressed

slave device, if ready to receive data, will respond by pulling the SD line low during the

9th clock pulse. This represents a so-called MCL acknowledge. The controller detecting

this affirmative acknowledge then opens a connection to the required slave. Data can

then be passed back and forth by the master controller, each 8-bit telegram being

acknowledged by the respective recipient. The communication is finally closed by the

master device and the slave device put back into standby by applying a stop condition

onto the bus.

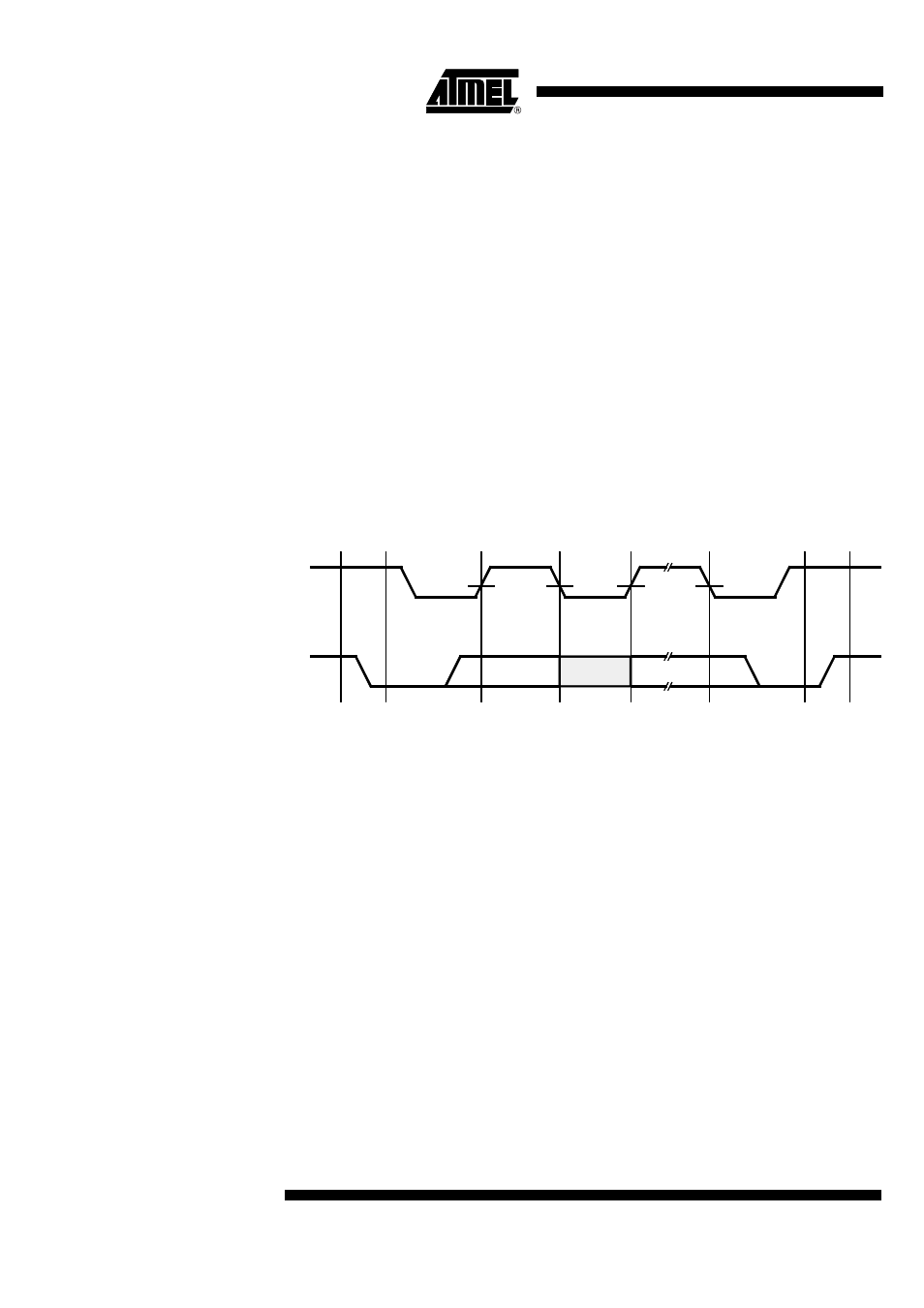

Figure 71.

MCL Bus Protocol 1

Bus not busy (1)

Both data and clock lines remain HIGH.

Start data transfer (2)

A HIGH to LOW transition of the SD line while the clock (SC)

is HIGH defines a START condition

Stop data transfer (3)

A LOW to HIGH transition of the SD line while the clock (SC)

is HIGH defines a STOP condition.

Data valid (4)

The state of the data line represents valid data when,

after START condition, the data line is stable for the

duration of the HIGH period of the clock signal.

Acknowledge

All address and data words are serially transmitted to and

from the device in eight-bit words. The receiving device

returns a zero on the data line during the ninth clock cycle to

acknowledge word receipt.

(2)

(1)

(4)

(4)

(3)

(1)

Start

condition

Data

valid

Data

change

Data

valid

Stop

condition

SC

SD