Bit synchronous mode, Atar862-8 – Rainbow Electronics ATAR862-8 User Manual

Page 68

68

ATAR862-8

4589B–4BMCU–02/03

All directional control of the external data port used by the SSI is handled automatically

and is dependent on the transmission direction set by the Serial Data Direction (SDD)

control bit. This control bit defines whether the SSI is currently operating in Transmit

(TX) mode or Receive (RX) mode.

Serial data is organized in 8-bit telegrams which are shifted with the most significant bit

first. In the 9-bit MCL mode, an additional acknowledge bit is appended to the end of the

telegram for handshaking purposes (see MCL protocol).

At the beginning of every telegram, the SSI control loads the transmit buffer into the shift

register and proceeds immediately to shift data serially out. At the same time, incoming

data is shifted into the shift register input. This incoming data is automatically loaded

into the receive buffer when the complete telegram has been received. Thus, data can

be simultaneously received and transmitted if required.

Before data can be transferred, the SSI must first be activated. This is performed by

means of the SSI reset control (SIR) bit. All further operation then depends on the data

directional mode (TX/RX) and the present status of the SSI buffer registers shown by

the Serial Interface Ready Status Flag (SRDY). This SRDY flag indicates the

(empty/full) status of either the transmit buffer (in TX mode), or the receive buffer (in RX

mode). The control logic ensures that data shifting is temporarily halted at any time, if

the appropriate receive/transmit buffer is not ready (SRDY = 0). The SRDY status will

then automatically be set back to ‘1’ and data shifting resumed as soon as the applica-

tion software loads the new data into the transmit register (in TX mode) or frees the shift

register by reading it into the receive buffer (in RX mode).

A further activity status (ACT) bit indicates the present status of the serial communica-

tion. The ACT bit remains high for the duration of the serial telegram or if MCL stop or

start conditions are currently being generated. Both the current SRDY and ACT status

can be read in the SSI status register. To deactivate the SSI, the SIR bit must be set

high.

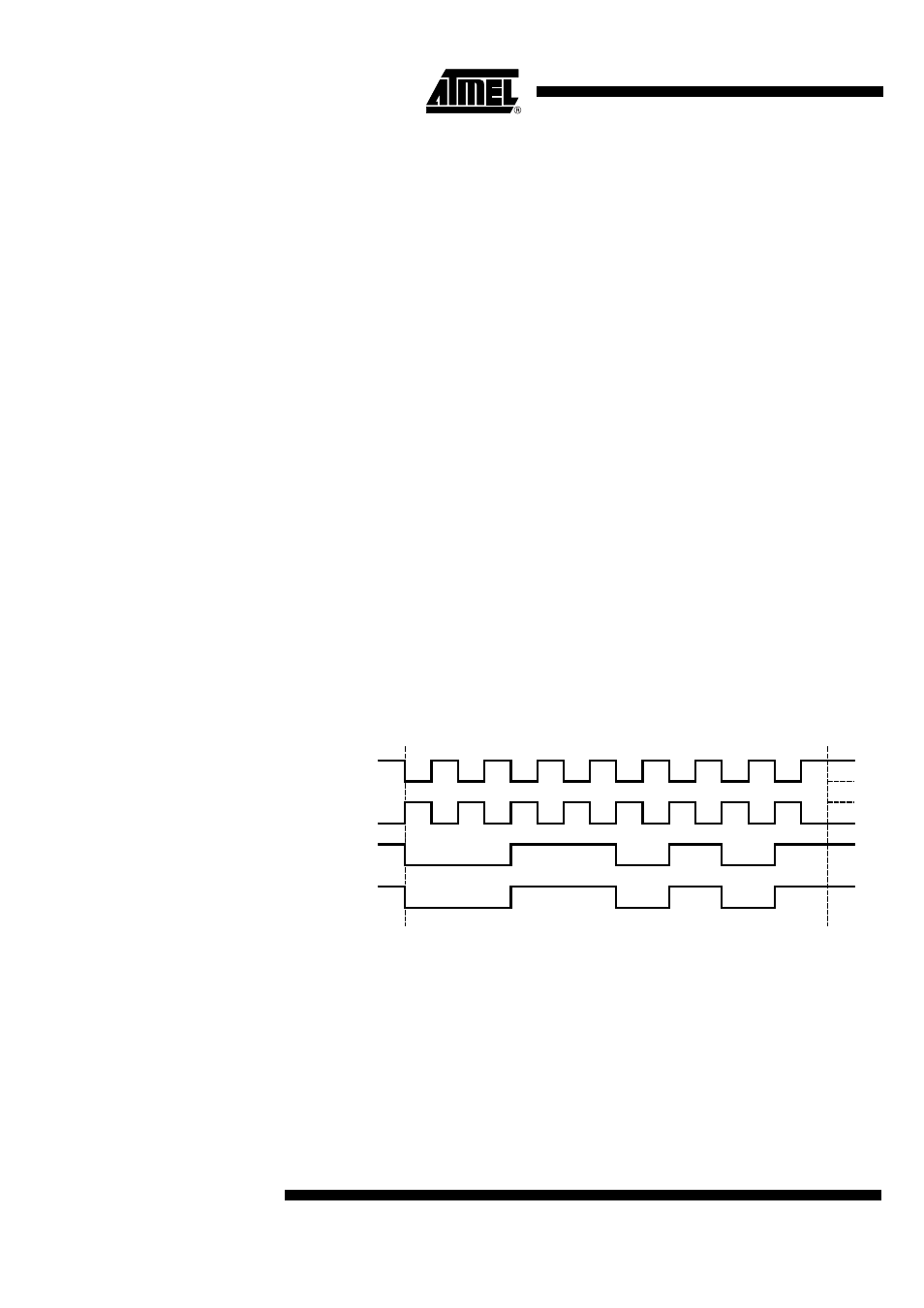

8-bit Synchronous Mode

Figure 66.

8-bit Synchronous Mode

In the 8-bit synchronous mode, the SSI can operate as either a 2- or 3-wire interface

(see SSI peripheral configuration). The serial data (SD) is received or transmitted in

NRZ format, synchronized to either the rising or falling edge of the shift clock (SC). The

choice of clock edge is defined by the Serial Mode Control bits (SM0,SM1). It should be

noted that

the transmission edge refers to the SC clock edge with which the SD

changes. To avoid clock skew problems, the incoming serial input data is shifted in with

the opposite edge.

When used together with one of the timer modulator or demodulator stages, the SSI

must be set in the 8-bit synchronous mode 1.

SC

SC

DATA

SD/TO2

1

1

0

1

0

1

0

0

Bit 7

Bit 0

1

1

0

1

0

1

0

0

Bit 7

Bit 0

Data: 00110101

(Rising edge)

(Falling edge)