Timer 2 modes, Mode 1: 12-bit compare counter, Atar862-8 – Rainbow Electronics ATAR862-8 User Manual

Page 45: Figure 37, Figure 38, Timer 2, Bit compare counter

45

ATAR862-8

4589B–4BMCU–02/03

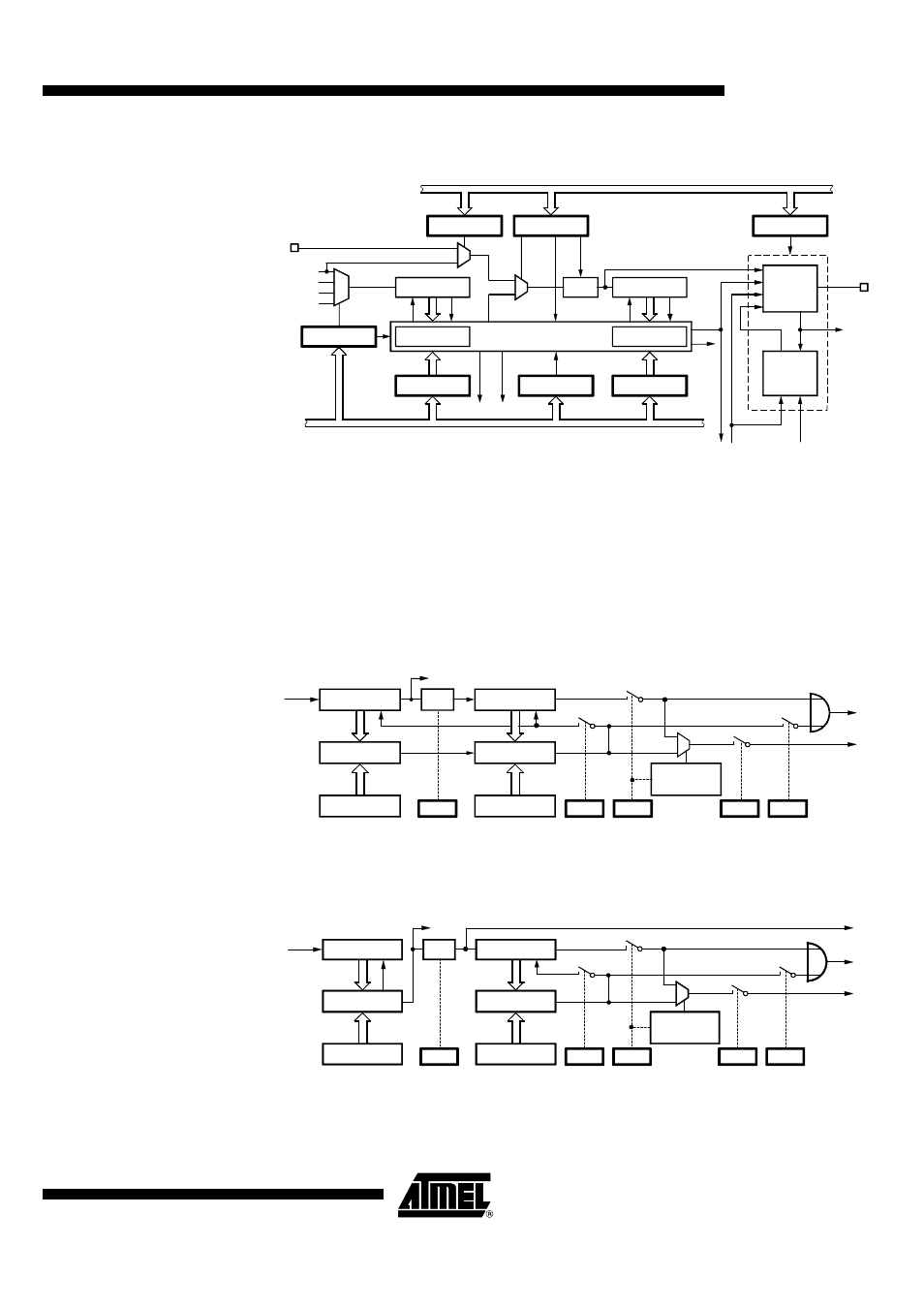

Figure 37.

Timer 2

Timer 2 Modes

Mode 1: 12-bit Compare

Counter

The 4-bit stage and the 8-bit stage work together as a 12-bit compare counter. A com-

pare match signal of the 4-bit and the 8-bit stage generates the signal for the counter

reset, toggle flip-flop or interrupt. The compare action is programmable via the compare

mode register (T2CM). The 4-bit counter overflow (OVF1) supplies the clock output

(POUT) with clocks. The duty cycle generator (DCG) has to be bypassed in this mode.

Figure 38.

12-bit Compare Counter

Mode 2: 8-bit Compare

Counter with 4-bit

Programmable Prescaler

Figure 39.

8-bit Compare Counter

4-bit Counter 2/1

RES

OVF1

Compare 2/1

T2CO1

CM1

POUT

SSI POUT

CL2/2

DCG

T2M1

P4CR

8-bit Counter 2/2

RES

OVF2

Compare 2/2

T2CO2

T2CM

Control

TOG2

INT4

Biphase-,

Manchester-

modulator

OUTPUT

MOUT

M2

to

Modulator 3

T2O

Timer 2

modulator

output-stage

T2M2

SO

Control

SSI

SSI

I/O-bus

T2C

CL2/1

T2I

SYSCL

T1OUT

TOG3

SCL

I/O-bus

DCGO

4-bit counter

4-bit compare

RES

4-bit register

CM1

POUT (CL2/1 /16)

8-bit counter

8-bit compare

8-bit register

OVF2

CM2

RES

T2RM

T2OTM

Timer 2

output mode

and T2OTM-bit

T2IM

T2CTM

TOG2

INT4

CL2/1

DCG

T2D1, 0

4-bit counter

4-bit compare

RES

4-bit register

CM1

POUT

8-bit counter

8-bit compare

8-bit register

OVF2

CM2

RES

T2RM

T2OTM

Timer 2

output mode

and T2OTM-bit

T2IM

T2CTM

TOG2

INT4

CL2/1

DCG

T2D1, 0

DCGO