Atar862-8, Figure 35, Figure 36 – Rainbow Electronics ATAR862-8 User Manual

Page 41

41

ATAR862-8

4589B–4BMCU–02/03

This timer starts running automatically after any power-on reset! If the watchdog func-

tion is not activated, the timer can be restarted by writing into the T1C1 register with

T1RM = 1.

Timer 1 can also be used as a watchdog timer to prevent a system from stalling. The

watchdog timer is a 3-bit counter that is supplied by a separate output of Timer 1. It gen-

erates a system reset when the 3-bit counter overflows. To avoid this, the 3-bit counter

must be reset before it overflows. The application software has to accomplish this by

reading the CWD register.

After power-on reset the watchdog must be activated by software in the $RESET initial-

ization routine. There are two watchdog modes, in one mode the watchdog can be

switched on and off by software, in the other mode the watchdog is active and locked.

This mode can only be stopped by carrying out a system reset.

The watchdog timer operation mode and the time interval for the watchdog reset can be

programmed via the watchdog control register (WDC).

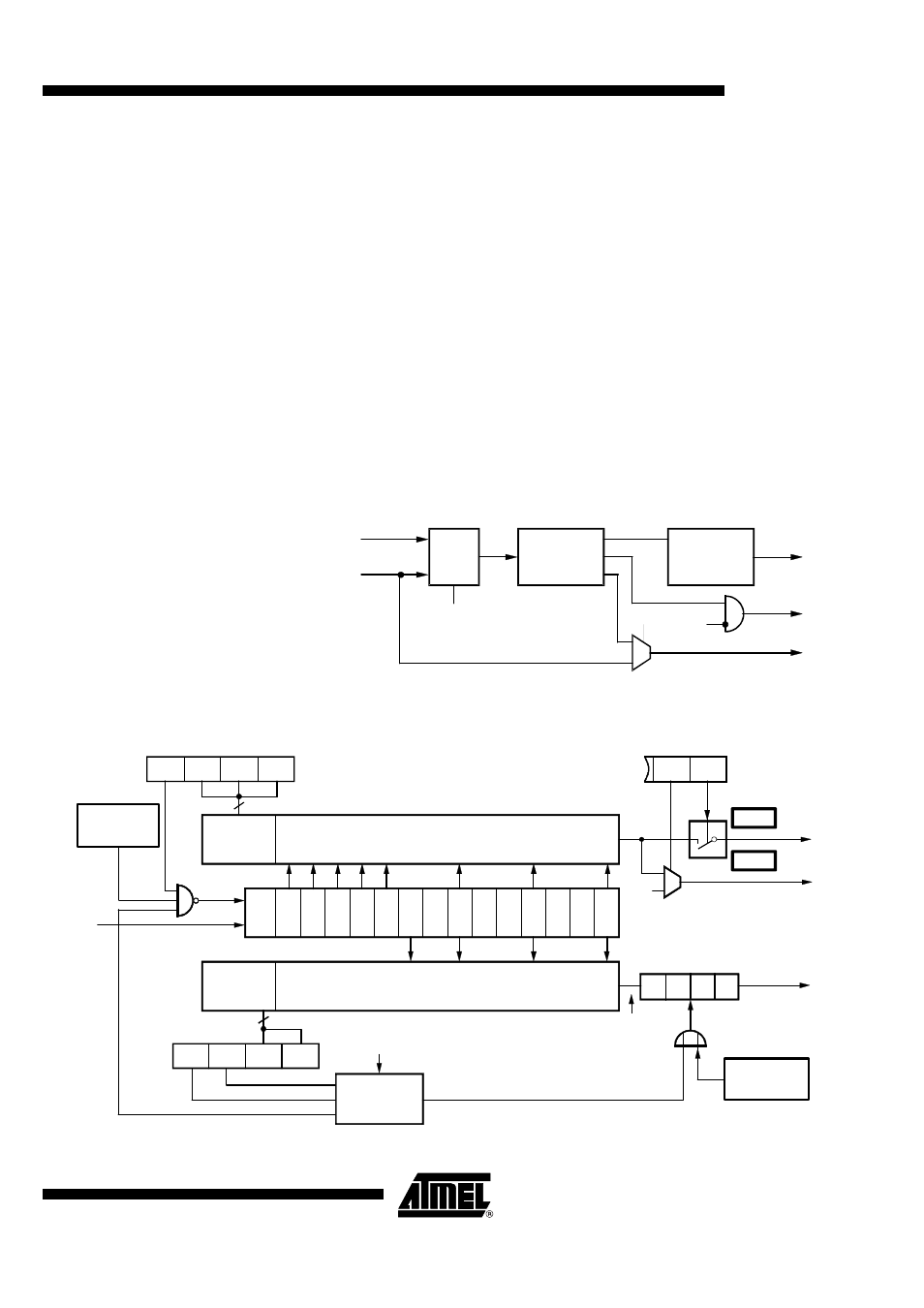

Figure 35.

Timer 1 Module

Figure 36.

Timer 1 and Watchdog

Prescaler

14 bit

CL1

Watchdog

4 bit

MUX

WDCL

T1IM

T1BP

T1MUX

NRST

INT2

T1OUT

T1CS

SYSCL

SUBCL

Q5

Q1 Q2

Q3 Q4

Q6

Q8

Q8

Q11

Q11

Q14

Q14

RES

CL

Decoder

Watchdog

mode control

MUX for interval timer

Decoder

MUX for watchdog timer

T1RM T1C2

T1C1

T1C0

3

2

WDL

WDR WDT1 WDT0

WDC

RES

T1MUX

SUBCL

T1BP T1IM

T1IM=0

T1IM=1

INT2

T1OUT

T1C2

RESET

(NRST)

Watchdog

Divider / 8

Divider

RESET

T1C1

Write of the

T1C1 register

CL1

WDCL

Read of the

CWD register