2 prr – power reduction register – Rainbow Electronics ATtiny43U User Manual

Page 35

35

8048B–AVR–03/09

• Bit 2 – BODSE: BOD Sleep Enable

BODSE enables setting of BODS control bit, as explained in BODS bit description. BOD disable

is controlled by a timed sequence.

7.5.2

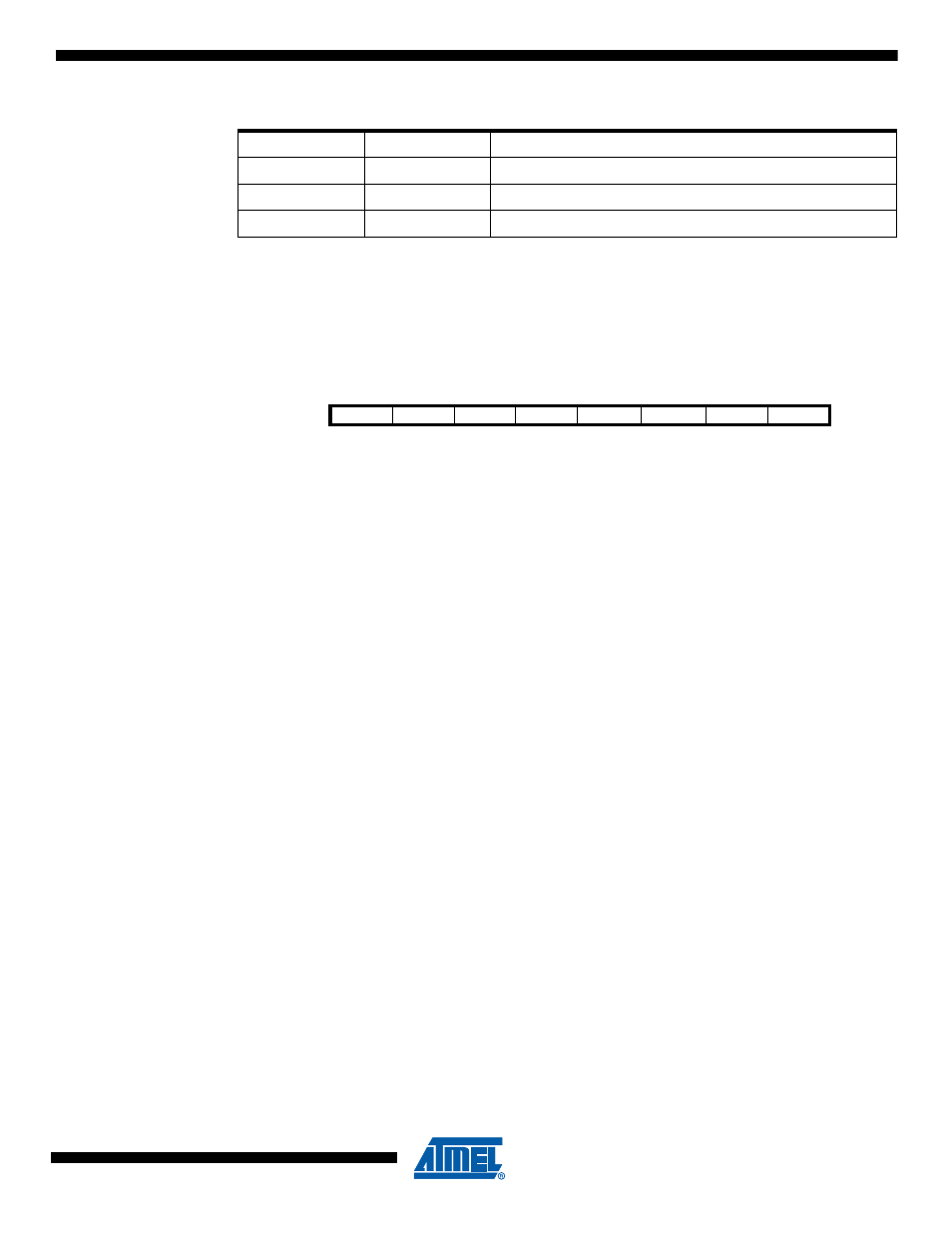

PRR – Power Reduction Register

• Bits 7:5 – PRE[2:0]: Prepared Read Enable

These bits are used for prepared read operations. See sections

“Software Control of Boost Con-

“ADCSRB – ADC Control and Status Register B” on page 47

• Bit 4 – Res: Reserved Bit

This bit is reserved and will always read zero.

• Bit 3 – PRTIM1: Power Reduction Timer/Counter1

Writing a logic one to this bit shuts down the Timer/Counter1 module. When the Timer/Counter1

is enabled, operation will continue like before the shutdown.

• Bit 2 – PRTIM0: Power Reduction Timer/Counter0

Writing a logic one to this bit shuts down the Timer/Counter0 module. When the Timer/Counter0

is enabled, operation will continue like before the shutdown.

• Bit 1 – PRUSI: Power Reduction USI

Writing a logic one to this bit shuts down the USI by stopping the clock to the module. When

waking up the USI again, the USI should be re-initialized to ensure proper operation.

• Bit 0 – PRADC: Power Reduction ADC

Writing a logic one to this bit shuts down the ADC. The ADC must be disabled before shut down.

The analog comparator cannot use the ADC input MUX when the ADC is shut down.

0

1

ADC Noise Reduction

1

0

Power-down

1

1

Reserved

Table 7-2.

Sleep Mode Select

SM1

SM0

Sleep Mode

Bit

7

6

5

4

3

2

1

0

PRE2

PRE1

PRE0

–

PRTIM1

PRTIM0

PRUSI

PRADC

PRR

Read/Write

R

R

R

R

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0