Attiny43u – Rainbow Electronics ATtiny43U User Manual

Page 118

118

8048B–AVR–03/09

ATtiny43U

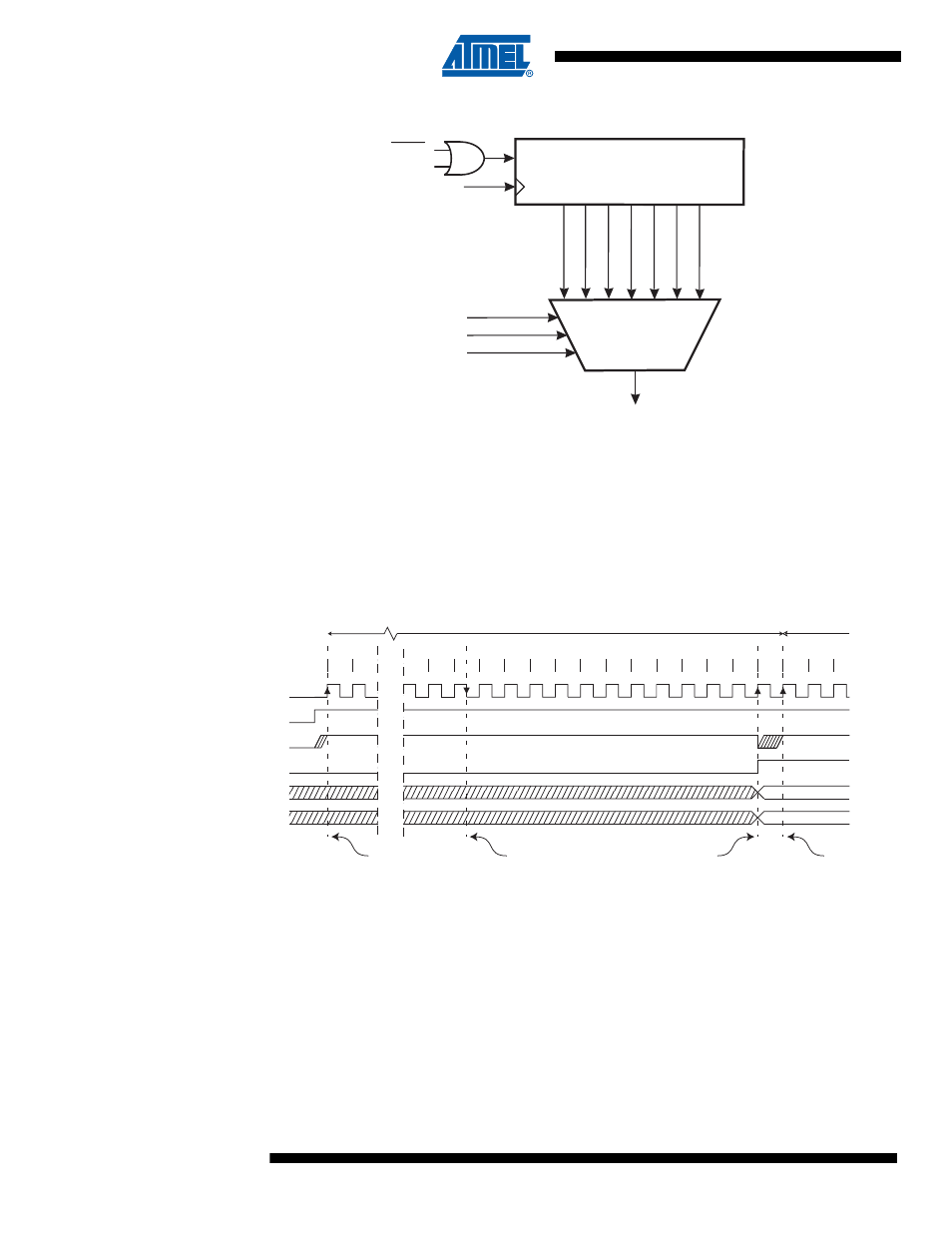

Figure 16-3. ADC Prescaler

When initiating a single ended conversion by setting the ADSC bit in ADCSRA, the conversion

starts at the following rising edge of the ADC clock cycle.

A normal conversion takes 13 ADC clock cycles, as summarised in

. The

first conversion after the ADC is switched on (ADEN in ADCSRA is set) takes 25 ADC clock

cycles in order to initialize the analog circuitry, as shown in

below.

Figure 16-4. ADC Timing Diagram, First Conversion (Single Conversion Mode)

The actual sample-and-hold takes place 1.5 ADC clock cycles after the start of a normal conver-

sion and 13.5 ADC clock cycles after the start of a first conversion. See

. When a

conversion is complete, the result is written to the ADC Data Registers, and ADIF is set. In Sin-

gle Conversion mode, ADSC is cleared simultaneously. The software may then set ADSC again,

and a new conversion will be initiated on the first rising ADC clock edge.

7-BIT ADC PRESCALER

ADC CLOCK SOURCE

CK

ADPS0

ADPS1

ADPS2

CK/128

CK/2

CK/4

CK/8

CK/16

CK/32

CK/64

Reset

ADEN

START

Sign and MSB of Result

LSB of Result

ADC Clock

ADSC

Sample & Hold

ADIF

ADCH

ADCL

Cycle Number

ADEN

1

2

12

13

14

15

16

17

18

19

20

21

22

23

24

25

1

2

First Conversion

Next

Conversion

3

MUX and REFS

Update

MUX and REFS

Update

Conversion

Complete