4 adc clock – clkadc, 2 clock sources, 1 external clock – Rainbow Electronics ATtiny43U User Manual

Page 24: Attiny43u

24

8048B–AVR–03/09

ATtiny43U

6.1.4

ADC Clock – clk

ADC

The ADC is provided with a dedicated clock domain. This allows halting the CPU and I/O clocks

in order to reduce noise generated by digital circuitry. This gives more accurate ADC conversion

results.

6.2

Clock Sources

The device has the following clock source options, selectable by Flash Fuse bits as shown

below. The clock from the selected source is input to the AVR clock generator, and routed to the

appropriate modules.

Note:

1. For all fuses “1” means unprogrammed while “0” means programmed.

6.2.1

External Clock

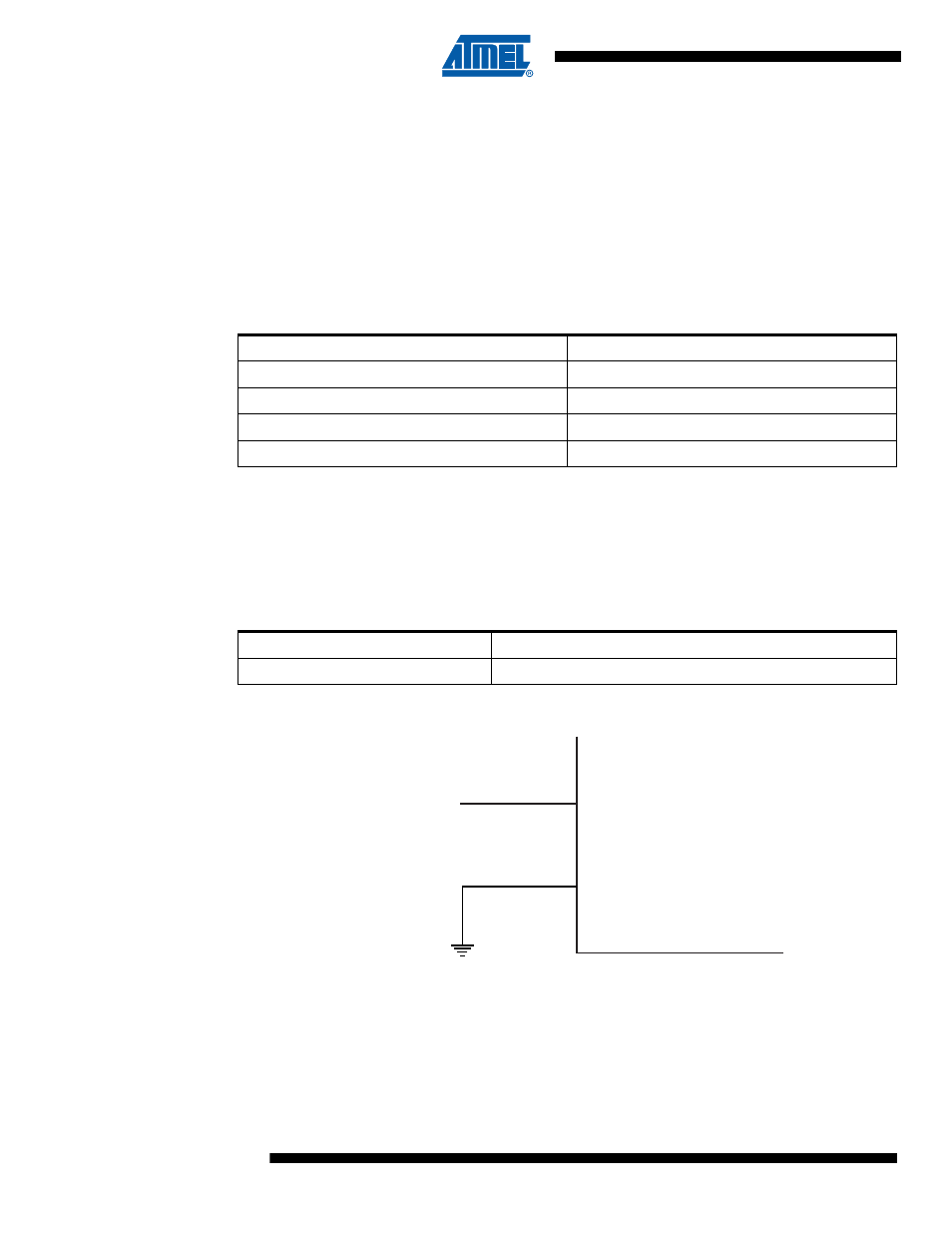

To drive the device from an external clock source, CLKI should be driven as shown in

. To run the device on an external clock, the CKSEL Fuses must be programmed to

“0000” (see

).

Figure 6-2.

External Clock Drive Configuration

Table 6-1.

Device Clocking Options Select

Device Clocking Option

CKSEL3..0

0000

Calibrated Internal 8 MHz Oscillator (see

)

0010

Internal 128 kHz Oscillator (see

)

0011

Reserved

0001, 0100-1111

Table 6-2.

Crystal Oscillator Clock Frequency

CKSEL3..0

Frequency

0000

0 - 8 MHz

EXTERNAL

CLOCK

SIGNAL

CLKI

GND