Adv ance informa tion, Signal groups description (continued) – Texas Instruments TMS320C6202 User Manual

Page 9

TMS320C6202

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS072B – AUGUST 1998 – REVISED AUGUST 1999

9

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251–1443

signal groups description (continued)

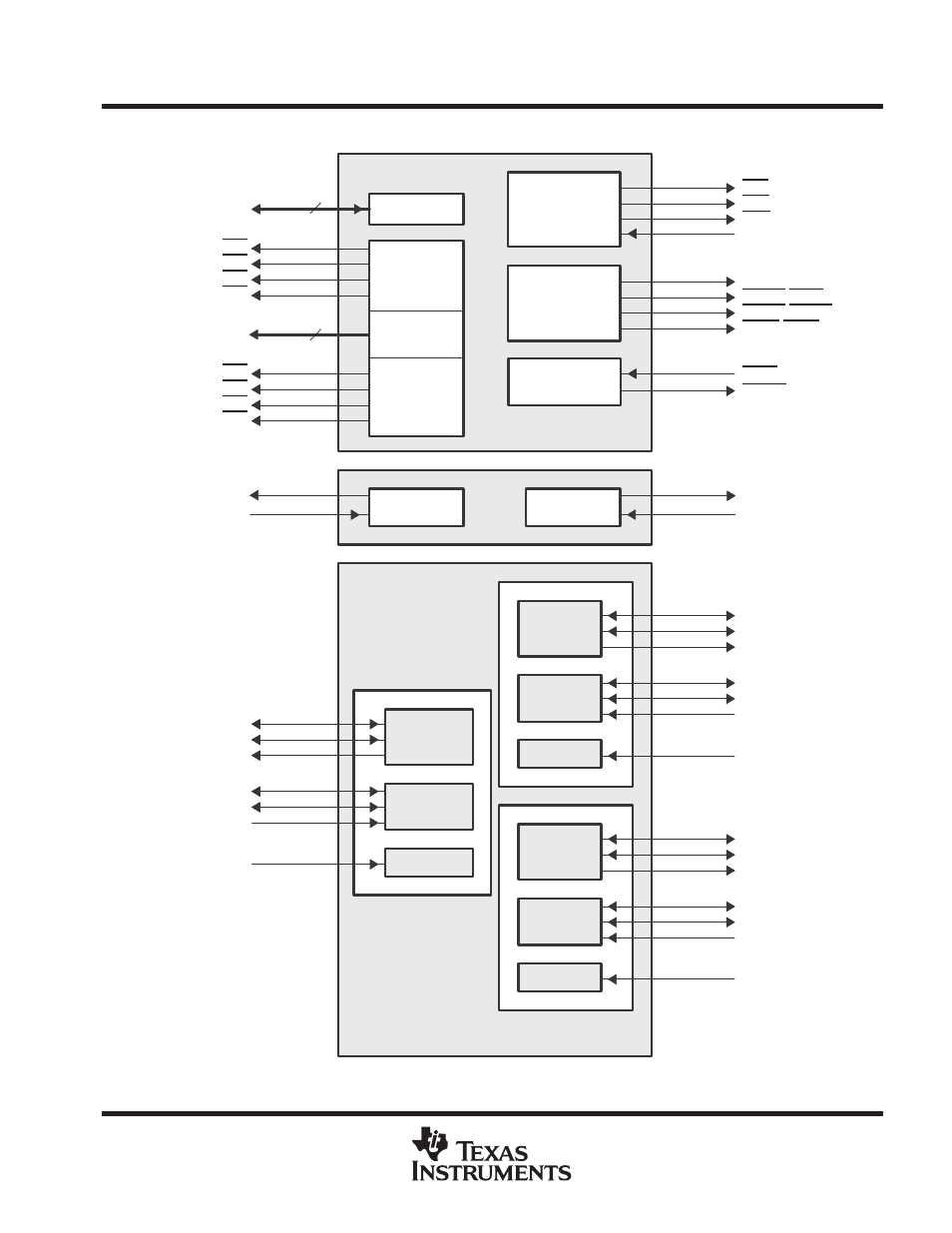

CE3

ARE

ED[31:0]

CE2

CE1

CE0

EA[21:2]

BE3

BE2

BE1

BE0

HOLD

HOLDA

TOUT1

CLKX1

FSX1

DX1

CLKR1

FSR1

DR1

CLKS1

AOE

AWE

ARDY

SDA10

SDRAS/SSOE

SDCAS/SSADS

SDWE/SSWE

TOUT0

CLKX2

FSX2

DX2

CLKR2

FSR2

DR2

CLKS2

Data

Memory Map

Space Select

Word Address

Byte Enables

HOLD/

HOLDA

32

20

Asynchronous

Memory

Control

Synchronous

Memory

Control

EMIF

(External Memory Interface)

Timer 1

Transmit

Transmit

Timer 0

Timers

McBSP1

McBSP2

Receive

Receive

Clock

Clock

McBSPs

(Multichannel Buffered Serial Ports)

TINP1

TINP0

CLKX0

FSX0

DX0

CLKR0

FSR0

DR0

CLKS0

Transmit

McBSP0

Receive

Clock

Figure 4. Peripheral Signals

ADV

ANCE INFORMA

TION