Adv ance informa tion, Switching characteristics during reset, See figure 24) – Texas Instruments TMS320C6202 User Manual

Page 42

TMS320C6202

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS072B – AUGUST 1998 – REVISED AUGUST 1999

42

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251–1443

RESET TIMING

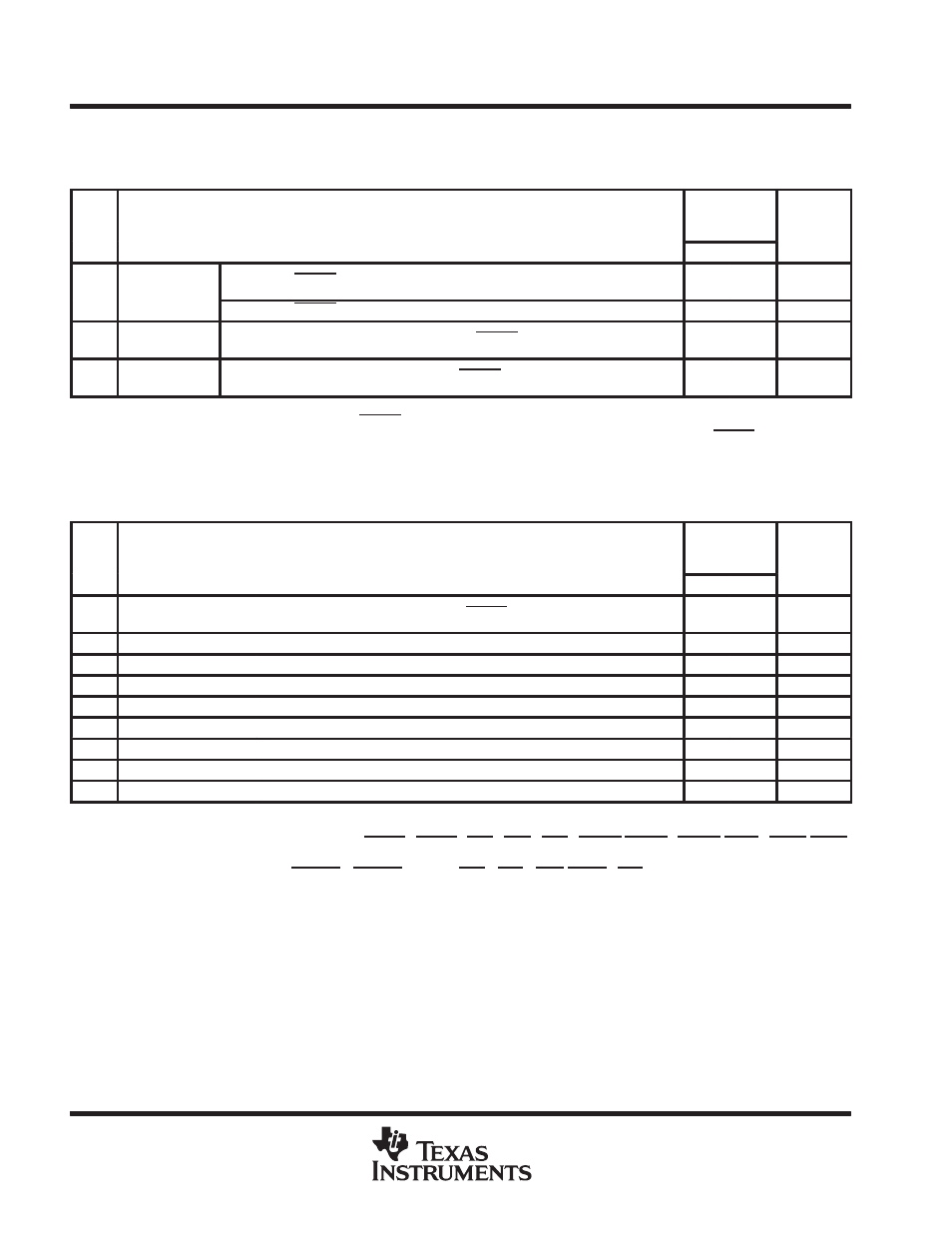

timing requirements for reset (see Figure 24)

NO.

’C6202-200

’C6202-233

’C6202-250

UNIT

MIN

MAX

1

tw(RST)

Width of the RESET pulse (PLL stable)†

10

CLKOUT1

cycles

w(RST)

Width of the RESET pulse (PLL needs to sync up)‡

250

µ

s

11

tsu(XD)

Setup time, XD configuration bits valid before RESET high§

5

CLKOUT1

cycles

12

th(XD)

Hold time, XD configuration bits valid after RESET high§

5

CLKOUT1

cycles

† This parameter applies to CLKMODE x1 when CLKIN is stable and applies to CLKMODE x4 when CLKIN and PLL are stable.

‡ This parameter only applies to CLKMODE x4. The RESET signal is not connected internally to the clock PLL circuit. The PLL, however, may

need up to 250

µ

s to stabilize following device power up or after PLL configuration has been changed. During that time, RESET must be asserted

to ensure proper device operation. See the

clock PLL section for PLL lock times.

§ XD[31:0] are the boot configuration pins during device reset.

switching characteristics during reset

¶

(see Figure 24)

NO.

PARAMETER

’C6202-200

’C6202-233

’C6202-250

UNIT

MIN

MAX

2

tR(RST)

Response time to change of value in RESET signal

2

CLKOUT1

cycles

3

td(CKO1H-CKO2IV)

Delay time, CLKOUT1 high to CLKOUT2 invalid

–1

10

ns

4

td(CKO1H-CKO2V)

Delay time, CLKOUT1 high to CLKOUT2 valid

–1

10

ns

5

td(CKO1H-XFCKIV)

Delay time, CLKOUT1 high to high group invalid

–1

10

ns

6

td(CKO1H-XFCKV)

Delay time, CLKOUT1 high to high group valid

–1

10

ns

7

td(CKO1H-LOWIV)

Delay time, CLKOUT1 high to low group invalid

–1

10

ns

8

td(CKO1H-LOWV)

Delay time, CLKOUT1 high to low group valid

–1

10

ns

9

td(CKO1H-ZHZ)

Delay time, CLKOUT1 high to Z group high impedance

–1

10

ns

10

td(CKO1H-ZV)

Delay time, CLKOUT1 high to Z group valid

–1

10

ns

¶ High group consists of:

XFCLK

Low group consists of:

IACK, INUM[3:0], DMAC[3:0], PD, TOUT0, and TOUT1

Z group consists of:

EA[21:2], ED[31:0], CE[3:0], BE[3:0], ARE, AWE, AOE, SDCAS/SSADS, SDRAS/SSOE, SDWE/SSWE,

SDA10, CLKX0, CLKX1, CLKX2, FSX0, FSX1, FSX2, DX0, DX1, DX2, CLKR0, CLKR1, CLKR2, FSR0, FSR1,

FSR2, XCE[3:0], XBE[3:0]/XA[5:2], XOE, XRE, XWE/XWAIT, XAS, XW/R, XRDY, XBLAST, XHOLD,

and XHOLDA

ADV

ANCE INFORMA

TION