Adv ance informa tion – Texas Instruments TMS320C6202 User Manual

Page 52

TMS320C6202

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS072B – AUGUST 1998 – REVISED AUGUST 1999

52

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251–1443

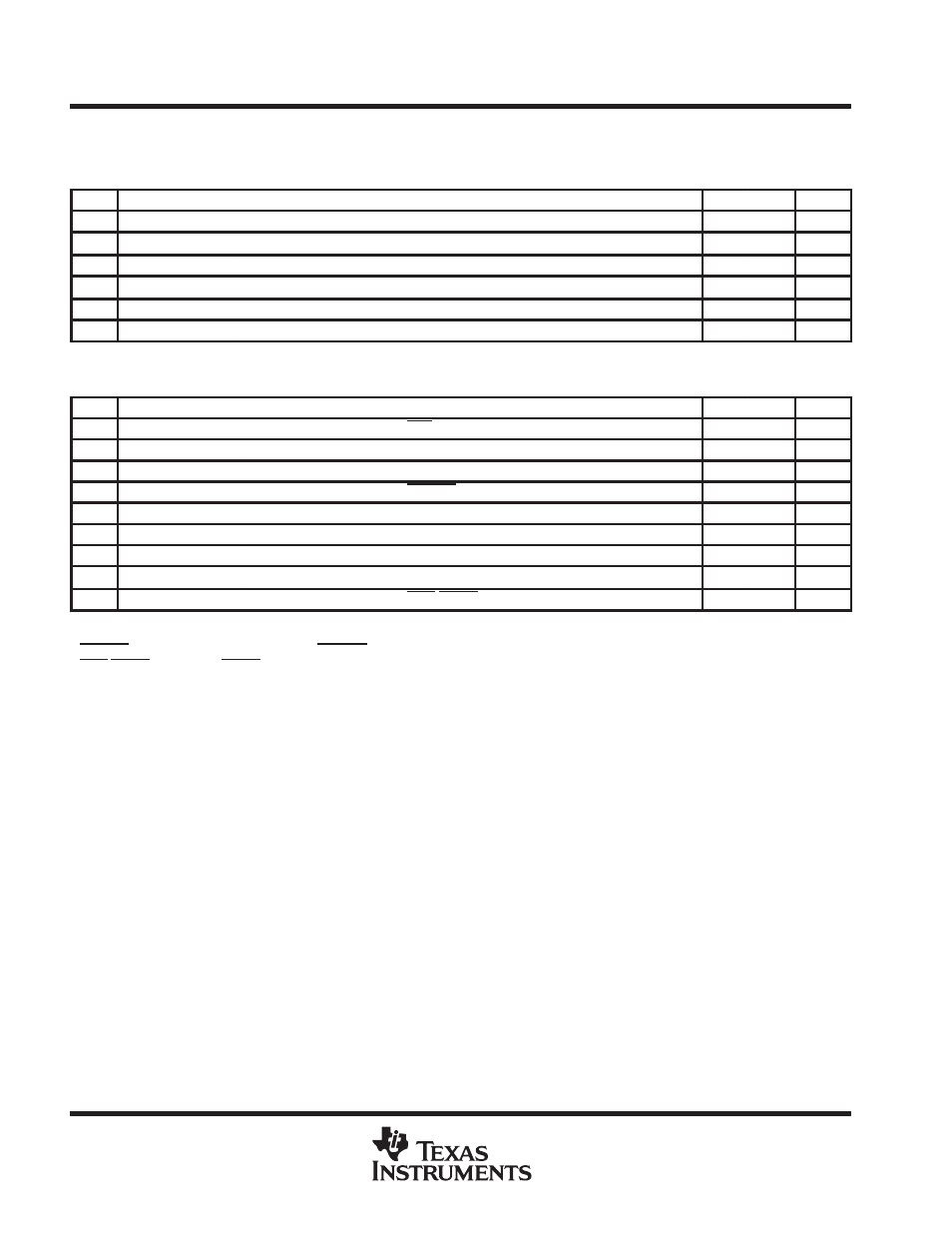

EXPANSION BUS SYNCHRONOUS HOST PORT TIMING (CONTINUED)

timing requirements with ’C6202 as bus master (see Figure 33, Figure 34, and Figure 35)

NO.

MIN

MAX

UNIT

9

tsu(XDV-XCKIH)

Setup time, XDx valid before XCLKIN high

4

ns

10

th(XCKIH-XDV)

Hold time, XDx valid after XCLKIN high

2.3

ns

11

tsu(XRY-XCKIH)

Setup time, XRDY valid before XCLKIN high†

4

ns

12

th(XCKIH-XRY)

Hold time, XRDY valid after XCLKIN high†

2.3

ns

14

tsu(XBFF-XCKIH)

Setup time, XBOFF valid before XCLKIN high

4

ns

15

th(XCKIH-XBFF)

Hold time, XBOFF valid after XCLKIN high

2.3

ns

† XRDY operates as active-low ready input/output during host-port accesses.

switching characteristics with ’C6202 as bus master (see Figure 33, Figure 34, and Figure 35)

NO.

PARAMETER

MIN

MAX

UNIT

1

td(XCKIH-XASV)

Delay time, XCLKIN high to XAS valid

5

15.5

ns

2

td(XCKIH-XWRV)

Delay time, XCLKIN high to XW/R valid‡

5

15.5

ns

3

td(XCKIH-XBLTV)

Delay time, XCLKIN high to XBLAST valid§

5

15.5

ns

4

td(XCKIH-XBEV)

Delay time, XCLKIN high to XBE[3:0]/XA[5:2] valid¶

5

15.5

ns

5

td(XCKIH-XDLZ)

Delay time, XCLKIN high to XDx low impedance

5

ns

6

td(XCKIH-XDV)

Delay time, XCLKIN high to XDx valid

15.5

ns

7

td(XCKIH-XDIV)

Delay time, XCLKIN high to XDx invalid

5

ns

8

td(XCKIH-XDHZ)

Delay time, XCLKIN high to XDx high impedance

18

ns

13

td(XCKIH-XWTV)

Delay time, XCLKIN high to XWE/XWAIT valid#

5

15.5

ns

‡ XW/R input/output polarity selected at boot.

§ XBLAST output polarity is always active low.

¶ XBE[3:0]/XA[5:2] operates as byte enables XBE[3:0] during host-port accesses.

# XWE/XWAIT operates as XWAIT output signal during host-port accesses.

ADV

ANCE INFORMA

TION