Adv ance informa tion – Texas Instruments TMS320C6202 User Manual

Page 36

TMS320C6202

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS072B – AUGUST 1998 – REVISED AUGUST 1999

36

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251–1443

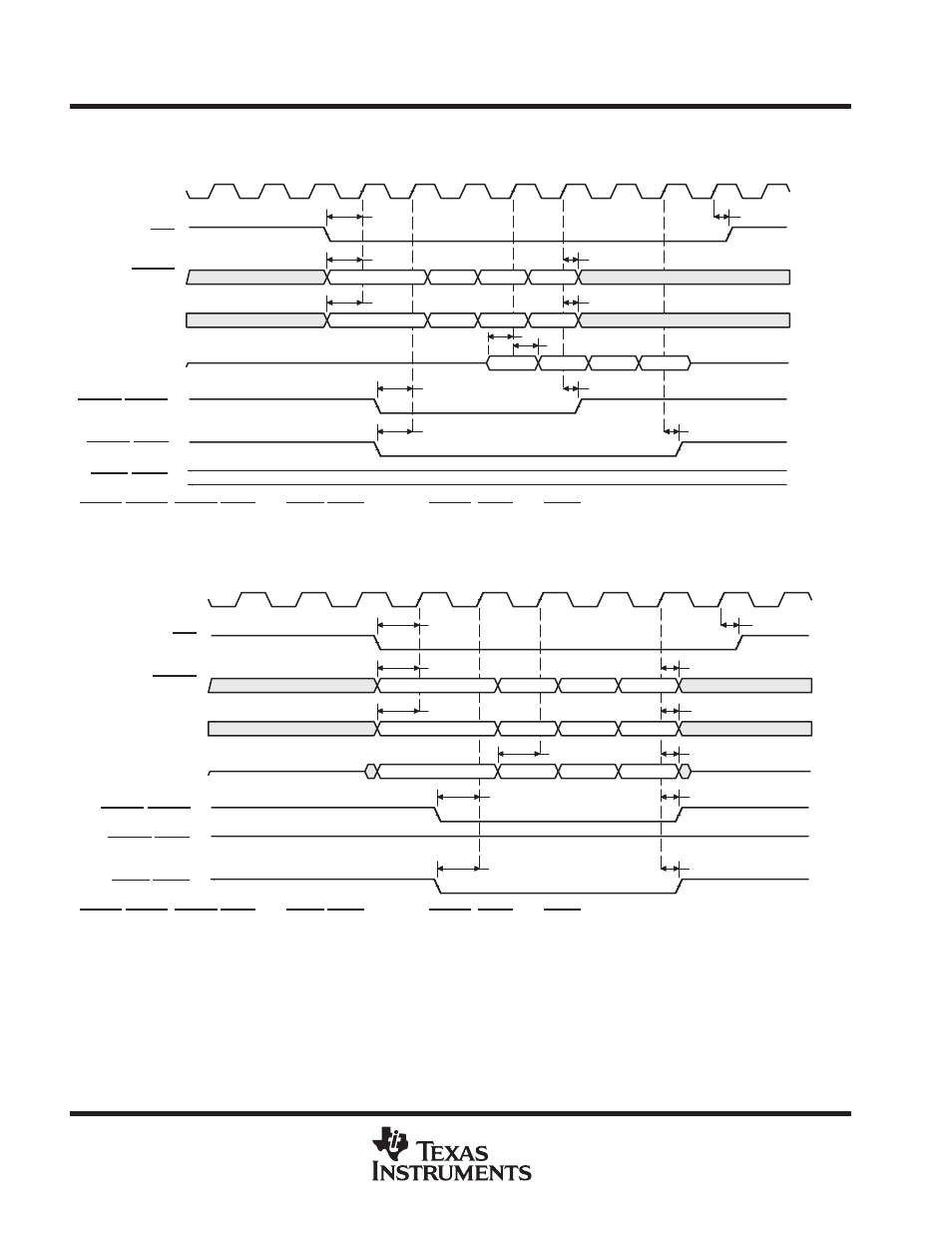

SYNCHRONOUS-BURST MEMORY TIMING (CONTINUED)

CLKOUT2

CEx

BE[3:0]

EA[21:2]

ED[31:0]

SDCAS/SSADS†

SDRAS/SSOE†

SDWE/SSWE†

BE1

BE2

BE3

BE4

A1

A2

A3

A4

Q1

Q2

Q3

Q4

12

11

10

9

6

5

4

3

2

1

8

7

† SDCAS/SSADS, SDRAS/SSOE, and SDWE/SSWE operate as SSADS, SSOE, and SSWE, respectively, during SBSRAM accesses.

Figure 15. SBSRAM Read Timing

CLKOUT2

CEx

BE[3:0]

EA[21:2]

ED[31:0]

SDRAS/SSOE†

SDWE/SSWE†

SDCAS/SSADS†

BE1

BE2

BE3

BE4

A1

A2

A3

A4

Q1

Q2

Q3

Q4

16

15

10

9

14

13

6

5

4

3

2

1

† SDCAS/SSADS, SDRAS/SSOE, and SDWE/SSWE operate as SSADS, SSOE, and SSWE, respectively, during SBSRAM accesses.

Figure 16. SBSRAM Write Timing

ADV

ANCE INFORMA

TION