Adv ance informa tion, See figure 13 – figure 14) – Texas Instruments TMS320C6202 User Manual

Page 33

TMS320C6202

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS072B – AUGUST 1998 – REVISED AUGUST 1999

33

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251–1443

ASYNCHRONOUS MEMORY TIMING

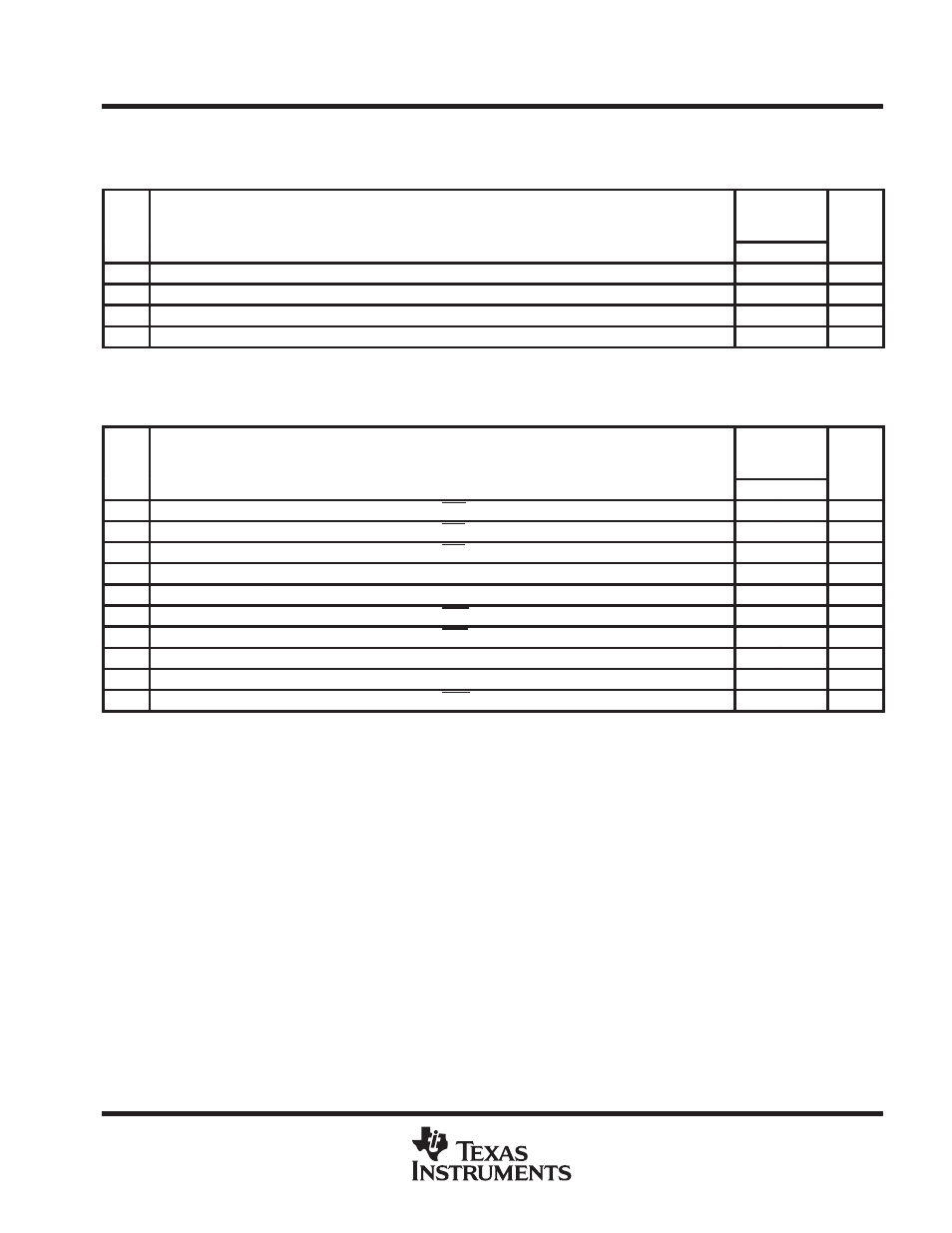

timing requirements for asynchronous memory cycles

†

(see Figure 13 – Figure 14)

NO.

’C6202-200

’C6202-233

’C6202-250

UNIT

MIN

MAX

6

tsu(EDV-CKO1H)

Setup time, read EDx valid before CLKOUT1 high

4.0

ns

7

th(CKO1H-EDV)

Hold time, read EDx valid after CLKOUT1 high

0

ns

10

tsu(ARDY-CKO1H)

Setup time, ARDY valid before CLKOUT1 high

4.0

ns

11

th(CKO1H-ARDY)

Hold time, ARDY valid after CLKOUT1 high

0

ns

† To ensure data setup time, simply program the strobe width wide enough. ARDY is internally synchronized. If ARDY does meet setup or hold

time, it may be recognized in the current cycle or the next cycle. Thus, ARDY can be an asynchronous input.

switching characteristics for asynchronous memory cycles

‡

(see Figure 13 – Figure 14)

NO.

PARAMETER

’C6202-200

’C6202-233

’C6202-250

UNIT

MIN

MAX

1

td(CKO1H-CEV)

Delay time, CLKOUT1 high to CEx valid

0

4.0

ns

2

td(CKO1H-BEV)

Delay time, CLKOUT1 high to BEx valid

0

4.0

ns

3

td(CKO1H-BEIV)

Delay time, CLKOUT1 high to BEx invalid

0

4.0

ns

4

td(CKO1H-EAV)

Delay time, CLKOUT1 high to EAx valid

0

4.0

ns

5

td(CKO1H-EAIV)

Delay time, CLKOUT1 high to EAx invalid

0

4.0

ns

8

td(CKO1H-AOEV)

Delay time, CLKOUT1 high to AOE valid

0

4.0

ns

9

td(CKO1H-AREV)

Delay time, CLKOUT1 high to ARE valid

0

4.0

ns

12

td(CKO1H-EDV)

Delay time, CLKOUT1 high to EDx valid

4.0

ns

13

td(CKO1H-EDIV)

Delay time, CLKOUT1 high to EDx invalid

0

ns

14

td(CKO1H-AWEV)

Delay time, CLKOUT1 high to AWE valid

0

4.0

ns

‡ The minimum delay is also the minimum output hold after CLKOUT1 high.

ADV

ANCE INFORMA

TION