Adv ance informa tion, See figure 38) – Texas Instruments TMS320C6202 User Manual

Page 57

TMS320C6202

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS072B – AUGUST 1998 – REVISED AUGUST 1999

57

POST OFFICE BOX 1443

•

HOUSTON, TEXAS 77251–1443

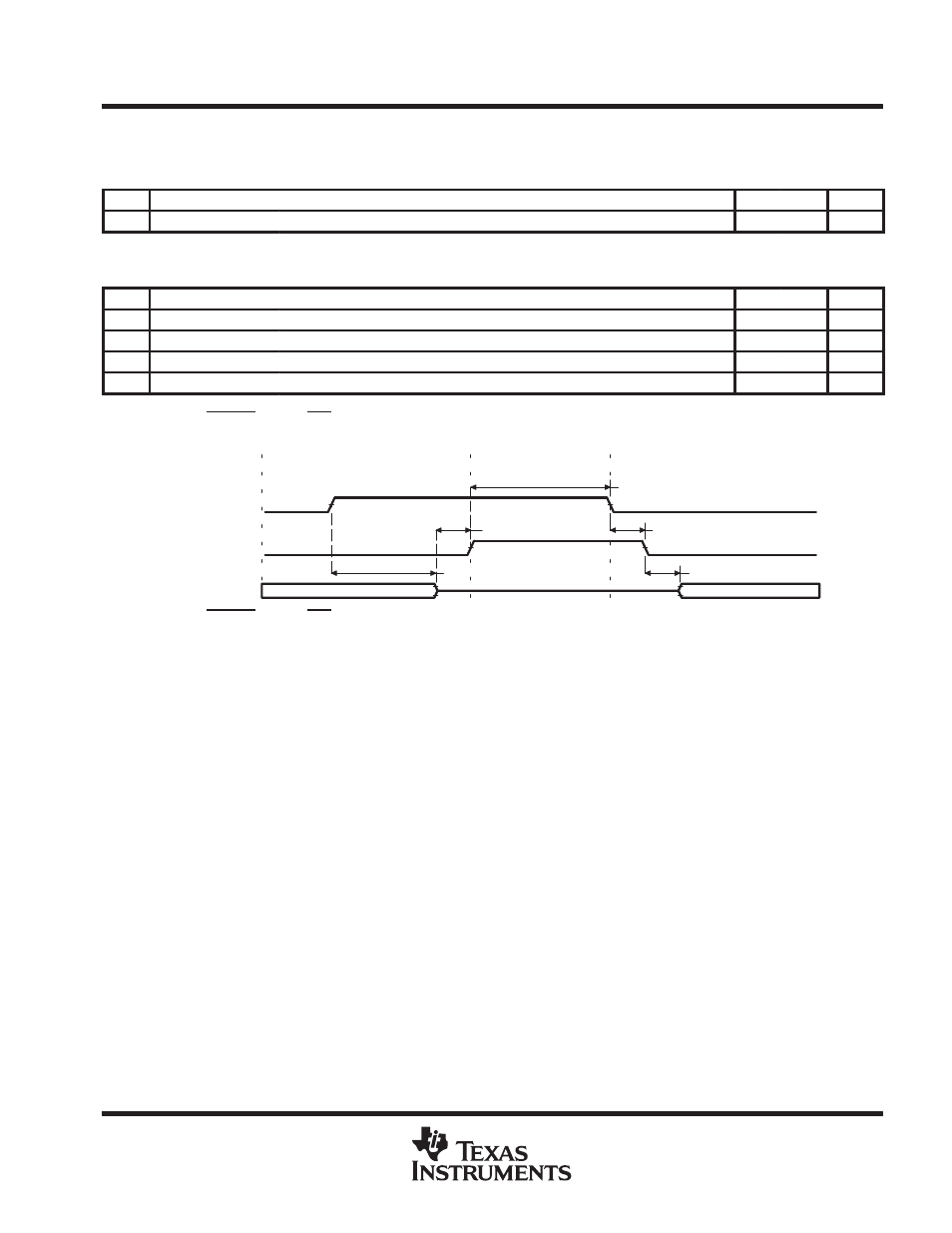

XHOLD/XHOLDA TIMING

timing requirements for expansion bus arbitration (internal arbiter enabled)

†

(see Figure 38)

NO.

MIN

MAX

UNIT

3

toh(XHDAH-XHDH)

Output hold time, XHOLD high after XHOLDA high

P

ns

† P = 1/CPU clock frequency in ns. For example, when running parts at 250 MHz, use P = 4 ns.

switching characteristics for expansion bus arbitration (internal arbiter enabled)

†‡

(see Figure 38)

NO.

PARAMETER

MIN

MAX

UNIT

1

tR(XHDH-XBHZ)

Response time, XHOLD high to XBus high impedance

4P

§

ns

2

td(XBHZ-XHDAH)

Delay time, XBus high impedance to XHOLDA high

0

2P

ns

4

tR(XHDL-XHDAL)

Response time, XHOLD low to XHOLDA low

4P

ns

5

td(XHDAL-XBLZ)

Delay time, XHOLDA low to XBus low impedance

0

2P

ns

† P = 1/CPU clock frequency in ns. For example, when running parts at 250 MHz, use P = 4 ns.

‡ XBus consists of XBE[3:0]/XA[5:2], XAS, XW/R, and XBLAST.

§ All pending XBus transactions are allowed to complete before XHOLDA is asserted.

2

DSP Owns Bus

External Requestor

DSP Owns Bus

C6202

C6202

5

1

4

3

XHOLD (input)

XHOLDA (output)

Owns Bus

XBus†

† XBus consists of XBE[3:0]/XA[5:2], XAS, XW/R, and XBLAST.

Figure 38. Expansion Bus Arbitration—Internal Arbiter Enabled

ADV

ANCE INFORMA

TION