5 using timer 2 – Texas Instruments MSC1210 User Manual

Page 87

Using Timer 2

8-13

Timers

It is important to note that the MSC1210 checks the P3.4 line each instruction

cycle (4 clock cycles). This means that if P3.4 is low, goes high, and goes back

low in 3 clock cycles, it will probably not be detected by the MSC1210. This also

means the MSC1210 event counter is only capable of counting events that occur

at a maximum of 1/8th the rate of the crystal frequency. That is to say, if the crystal

frequency is 12.000MHz, it can count a maximum of 1 500 000 events per second

(12.000MHz

S

1/8 = 1 500 000). If the event being counted occurs more than

1 500 000 times per second, the MSC1210 will not be able to accurately count

the event without using additional external circuitry or a faster crystal.

8.5

Using Timer 2

The MSC1210 has a third timer, Timer 2, which functions slightly differently

than Timers 0 and 1 and, for that reason, we are addressing this third timer sep-

arately from the first two.

8.5.1

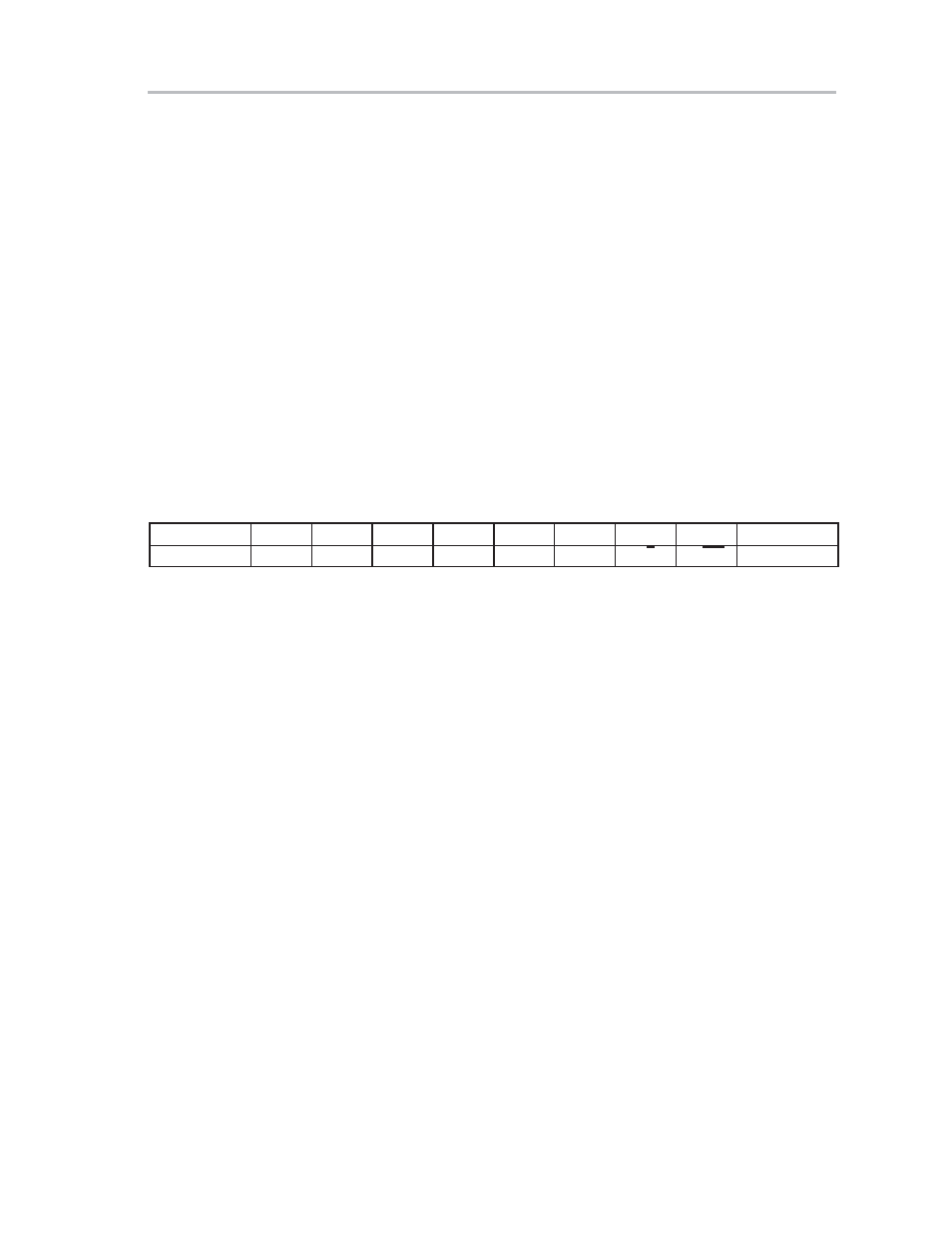

T2CON SFR

The operation of Timer 2 (T2) is controlled almost entirely by the T2CON SFR,

at address C8

H

. This SFR is bit-addressable because this SFR is evenly divis-

ible by eight.

The individual bits of T2CON have the following functions:

7

6

5

4

3

2

1

0

Reset Value

SFR C8H

TF2

EXF2

RCLK

TCLK

EXEN2

TR2

C/T

CP/RL2

00H

TF2 (bit 7)—Timer 2 Overflow Flag. This flag will be set when Timer 2 overflows

from FFFF

H

. It must be cleared by software. TF2 will only be set if RCLK and TCLK

are both cleared to 0. Writing a 1 to TF2 forces a Timer 2 interrupt if enabled.

EXF2 (bit 6) Timer 2 External Flag. A negative transition on the T2EX pin

(P1.1) will cause this flag to be set based on the EXEN2 (T2CON.3) bit. If set

by a negative transition, this flag must be cleared to 0 by software. Setting this

bit in software will force a timer interrupt, if enabled.

RCLK (bit 5)—Receive Clock Flag. This bit determines the serial Port 0 time-

base when receiving data in serial modes 1 or 3.

0 = Timer 1 overflow is used to determine receiver baud rate for serial Port 0.

1 = Timer 2 overflow is used to determine receiver baud rate for serial Port 0.

Setting this bit will force Timer 2 into baud rate generation mode. The timer will

operate from a divide by 2 of the external clock.

TCLK (bit 4)—Transmit Clock Flag. This bit determines the serial Port 0 timer

base when transmitting data in serial modes 1 or 3.

0 = Timer 1 overflow is used to determine transmitter baud rate for serial Port 0.

1 = Timer 2 overflow is used to determine transmitter baud rate for serial Port 0.

Setting this bit will force Timer 2 into baud rate generation mode. The timer will

operate from a divide by 2 of the external clock.

EXEN2 (bit 3)—Timer 2 External Enable. This bit enables the capture/reload

function on the T2EX pin if Timer 2 is not generating baud rates for the serial port.

0 = Timer 2 will ignore all external events at T2EX.

1 = Timer 2 will capture or reload a value if a negative transition is detected on

the T2EX pin.