Texas Instruments MSC1210 User Manual

Page 171

FIFO Operation

13-9

Serial Peripheral Interface (SPI)

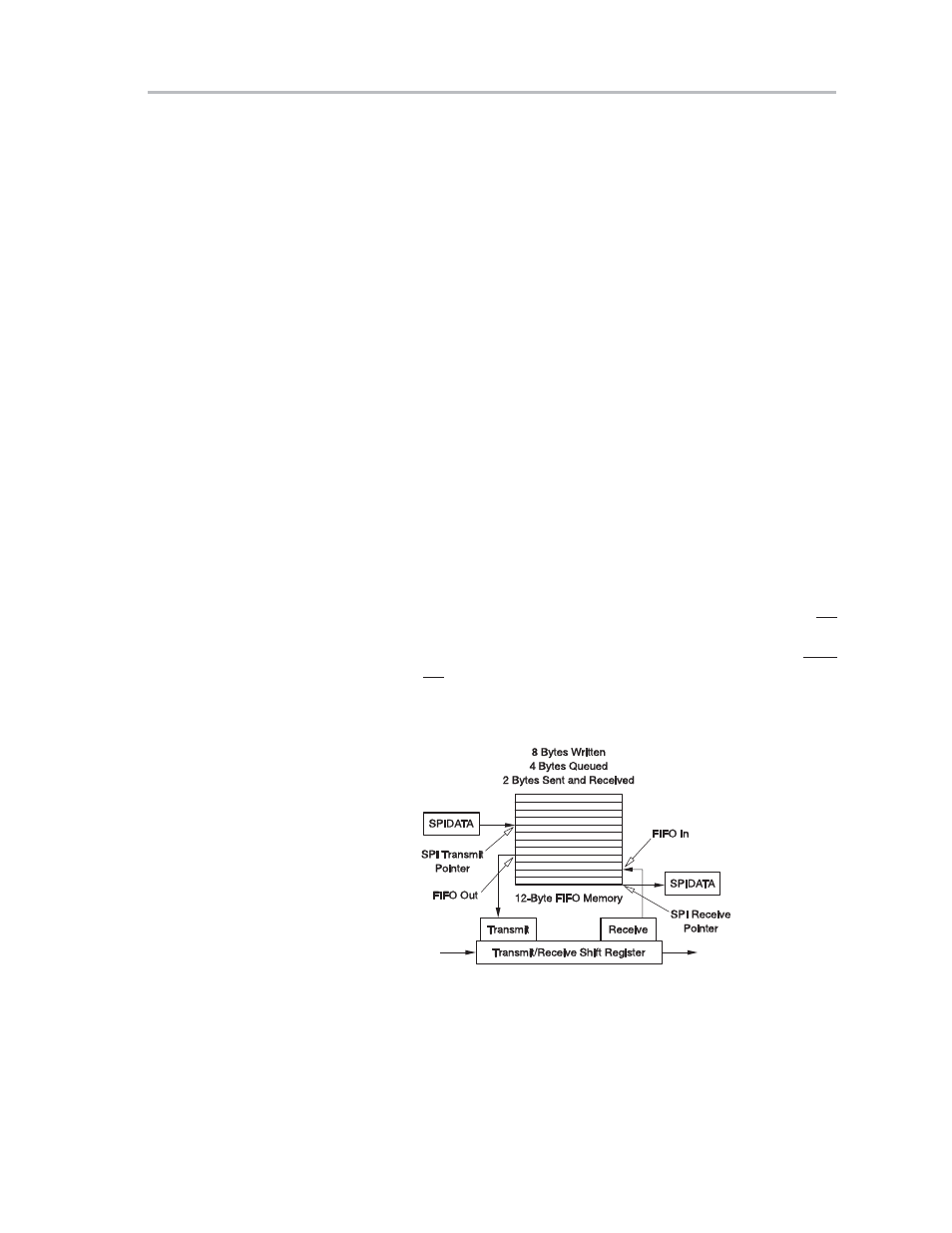

13.7 FIFO Operation

Data transmitted by the SPI interface is written to the SPIDATA register. If the

FIFO is enabled, it is stored in the FIFO memory. The first two bytes are

immediately written to the transmit buffer, and the SPI transmit pointer is

incremented. For each byte transmitted using the SCLK signal, a byte is also

received. The received bytes are immediately transferred to the FIFO. The

FIFO IN pointer increments for each byte received until one less than the SPI

received pointer. If the received bytes are not read or flushed, then additional

SCLKs will continue to send until the last byte is sent. Therefore, if the SPI is

used to only transmit bytes, the SPI receive interrupt can be used to flush the

received bytes so that transmission of data is not blocked.

The SPI interrupts can be used to achieve maximum throughput. The size of

the FIFO can be adjusted from 2 to 128 bytes depending on the allowable inter-

rupt latency. For example, assume that the application has time critical opera-

tions that cannot be interrupted for 10

µ

s. Using an 11.0592MHz crystal and if

SPI clock is f

OSC

/2, one byte can be shifted out in 1.46

µ

s, or 69 bytes in 100

µ

s.

By setting the transmit IRQ level for 8, it would require that the FIFO be at least

77 bytes. If not receiving bytes, but simply flushing the receive buffer, the IRQ

level for the receive interrupt has to be taken into account. For example, to al-

low the receive buffer to grow to 32 before generating an interrupt, add 32 to

the 69 transfers. That gives a minimum buffer size of 101. A FIFO of 100 bytes

would be adequate because two bytes are stored in the buffer register and shift

register.

When using the FIFO, there is no mechanism to remove and reassert the SS

line between each byte transferred, which is required for CPHA = 0. For slower

transfer rates, it is possible for the program to monitor the SCLK using INT5

and control the SS signal as needed.

Figure 13−4. SPI FIFO Operation