Texas Instruments MSC1210 User Manual

Page 164

Description

13-2

13.1 Description

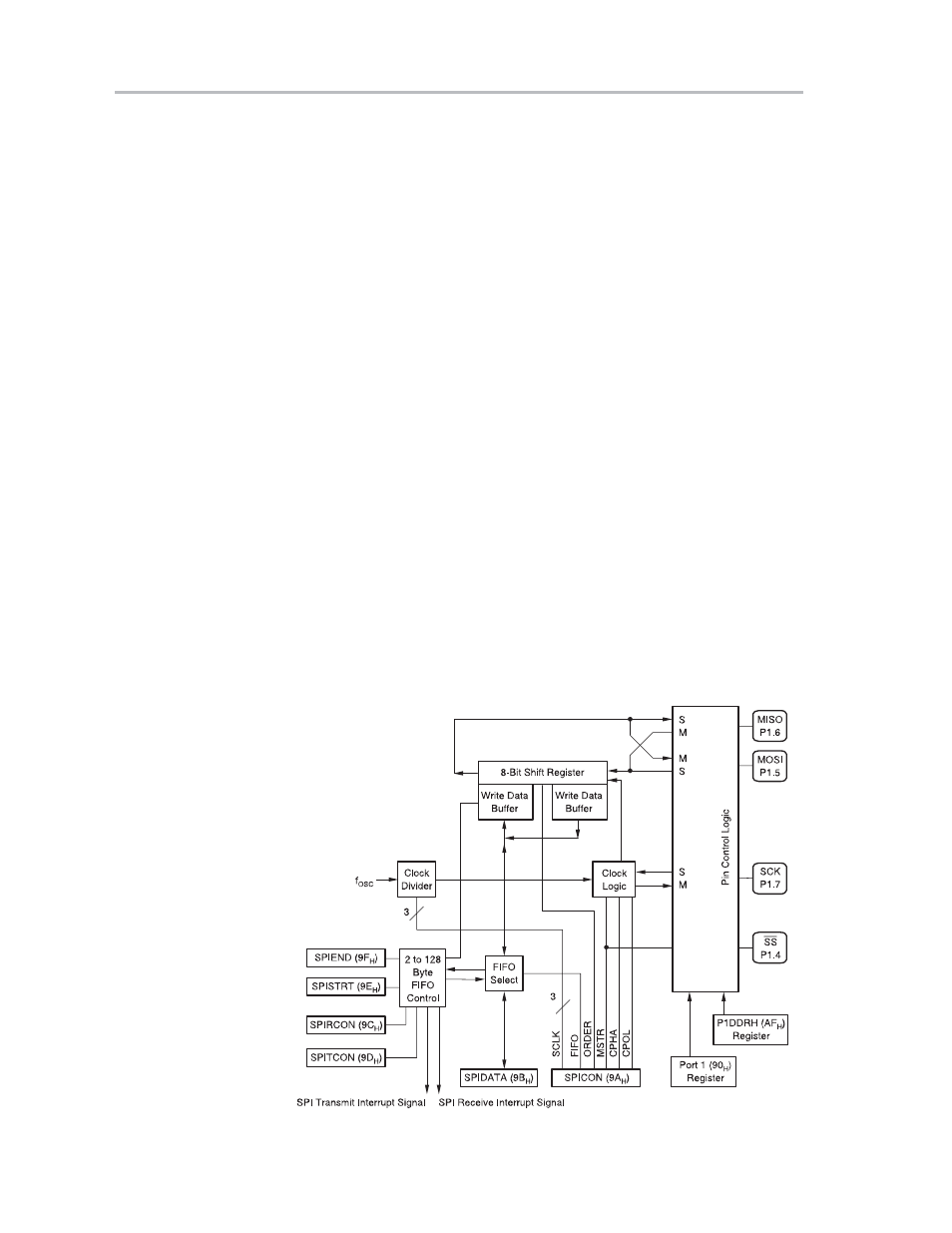

The MSC1210 includes a serial peripheral interface (SPI) module that allows

simple and efficient access to SPI-compatible devices via a number of SFRs

provided for that purpose. The SPI is an independent serial communications

subsystem that allows the MSC1210 to communicate synchronously with SPI

peripheral devices and other microprocessors. The SPI is also capable of

interprocessor communication in a multiple master system. The SPI system

can be configured as either a master or a slave device.

The maximum data transfer rates can be as high as 1/2 the f

OSC

clock rate

(12Mbits per second for a 24MHz f

OSC

frequency).

13.2 Functional Description

The central element in the SPI system is the block containing the shift register and

the read data buffer. SPI data is transmitted and received simultaneously. For

every byte that is sent, a byte is also received. The system is double-buffered in

the transmit direction and double-buffered in the receive direction. This means

that new data for transmission can be written to the SPIDATA register before the

previous transfer is complete. Additionally, received data is transferred into a

parallel read data buffer, so the shifter is free to accept a second serial character.

As long as the first character is read out of the SPIDATA register before the next

serial character is ready to be transferred, no overrun condition occurs.

For FIFO operation, the reading of the received data can be delayed up to the

length of time it takes to fill the FIFO. The SPIDATA register is used for reading

data received, and for writing data to be sent, as shown in Figure 13−1.

Figure 13−1. SPI block diagram