Texas Instruments MSC1210 User Manual

Page 169

Data Transfers

13-7

Serial Peripheral Interface (SPI)

13.6 Data Transfers

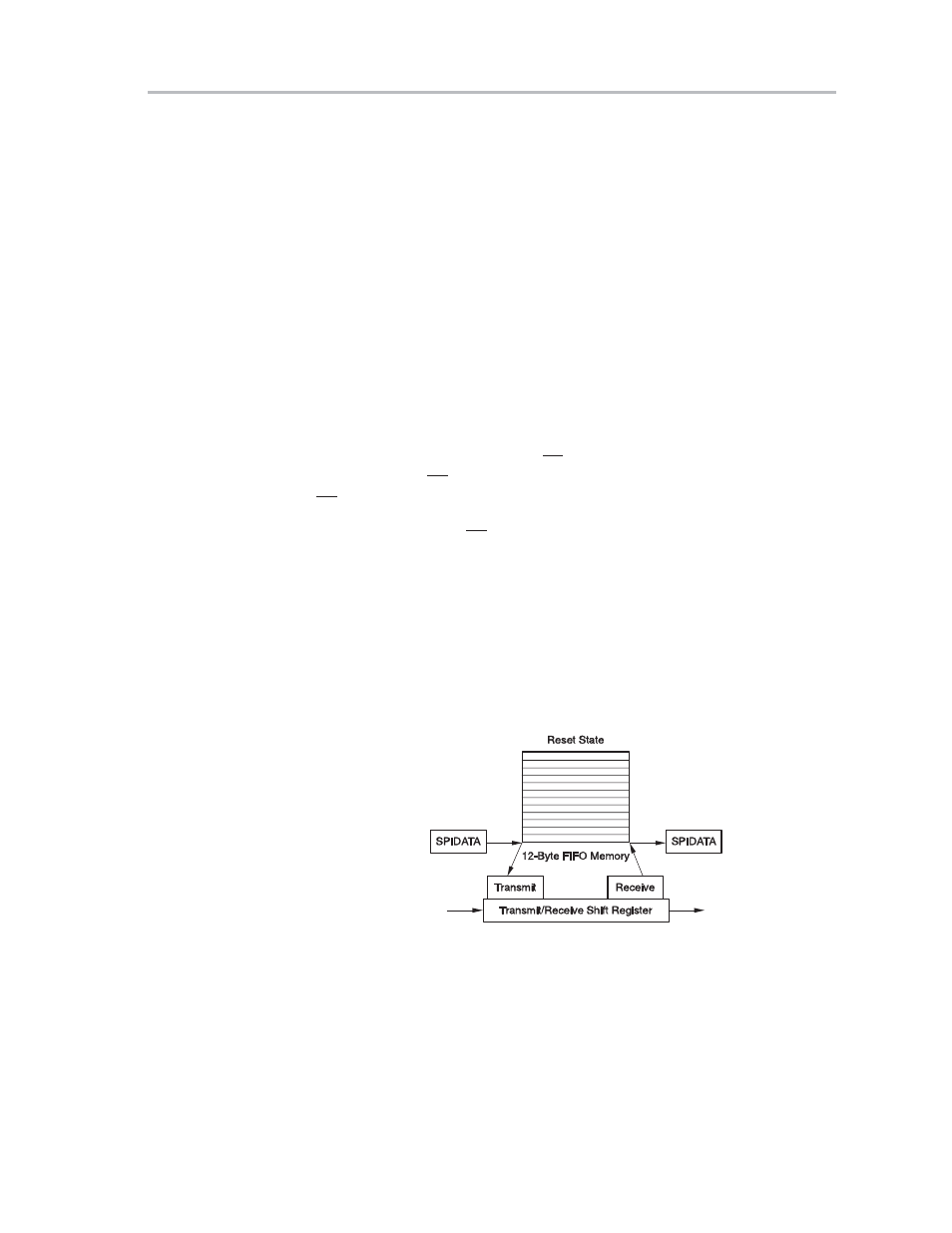

The transmitted and received data for SPI transfers are both double-buffered.

This means that a second byte can be written for transmit before the first byte

has been sent. Data that is received does not have to be read from the SPIDAT

register until just before the next byte is received. The size of this buffer can

essentially be extended with the FIFO mode. This adds from 2 to 128 bytes

of FIFO memory.

The FIFO mode uses a portion of the internal indirect RAM from 80

H

to FF

H

.

The start and end of the FIFO portion of memory is set with the SPISTRT (9E

H

)

and SPIEND (9F

H

) registers. The only restriction on those addresses is that

the value of SPIEND must be larger than SPISTRT. The most significant bit is

forced to a one.

There is no signal that switches the SPI interface on or off. It can be powered

down using the PDCON (F1

H

) register. However, if it is powered up, then it is

operational. For the master, all that is necessary to transmit a byte is to write

the value to SPIDATA (9B

H

). The SS pin is not used in master mode. It can be

used to drive an SS signal. For slave operation, the bytes will not transfer until

SS is asserted and the clock signals are received.

For slave mode, if the SS signal goes high while a byte is being received, that

byte is immediately flagged as completed and the interface is prepared for a

new byte.

The SPICON (9A

H

) register controls the SCLK frequency for master operation,

and has bits to enable the FIFO, master mode, set bit order, clock polarity and

phase. Any change to the SPICON register resets the SPI interface, and clears

the counters and pointers, as shown in Figure 13−3.

Figure 13−3. SPI Reset State