Texas Instruments MSC1210 User Manual

Page 71

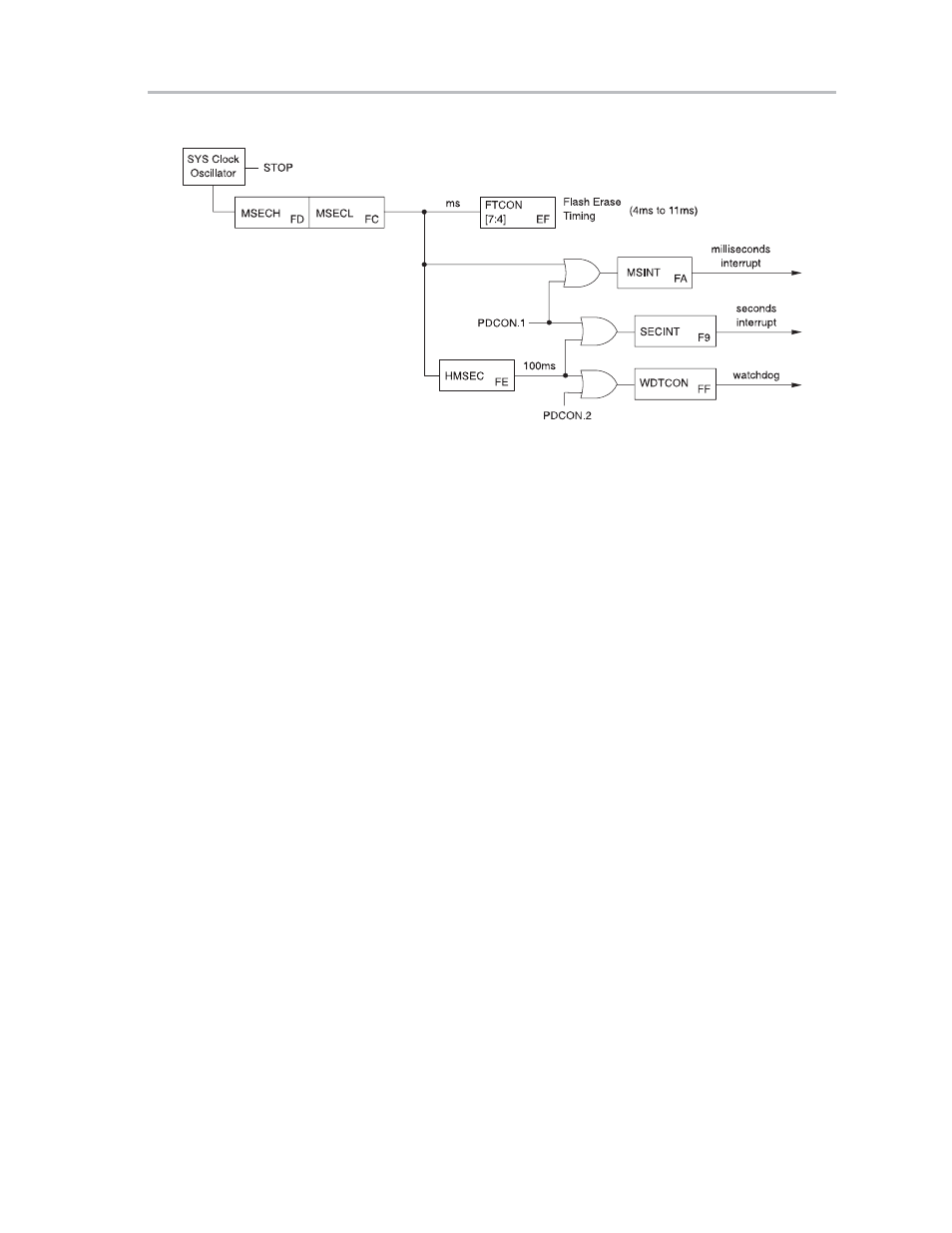

System Timers

7-7

System Timing

Figure 7−4. System Timing Interrupt Control

The MSECH (FD

H

) and MSECL (FC

H

) SFRs should be set to a value such that

the system clock divided by the value of these SFRs, plus one, generates a 1ms

clock. For example, given a system clock of 12.000MHz, MSECH/MSECL should

be set to 12 000 000 / 1000 = 12 000 – 1 = 11 999. Thus, for a 12.000MHz system

clock, MSECH/MSECL should be set to 11 999 to generate a 1ms clock.

In reality, the MSECH/MSECL SFRs may be set to a value that produces a

clock that is something other than 1ms. This works fine, as long as the other

timers that depend on the MSECH/MSECL SFR are adjusted accordingly.

7.2.2.1

Milliseconds Auxiliary Interrupt

The milliseconds interrupt is one of the auxiliary interrupts that may be used

by the user program. The milliseconds auxiliary interrupt is enabled by setting

EMSEC (AIE.4) and enabling auxiliary interrupts via the EAI (EICON.5) bit.

The frequency at which the milliseconds interrupt will be triggered is controlled

by the value written to the MSINT (FA

H

) SFR.

When enabled, a millisecond auxiliary interrupt will be triggered after MSINT + 1ms,

assuming that MSECH/MSECL have been configured to produce a correct

milliseconds clock. The value written to the MSINT SFR is a value between 0 and

127, meaning that the milliseconds interrupt may be triggered every 1ms to 128ms

(assuming a correct milliseconds clock).

For example, given an accurate milliseconds clock, setting MSINT to 5 would

produce a milliseconds auxiliary interrupt every 6ms.

Bit 7 of MSINT, when written, indicates whether the MSINT value being written

should be written immediately, or if it should be written after the current MSINT

count has expired. If bit 7 is set, MSINT will immediately be updated with the

new value; if it is clear, MSINT will be updated with the new value as soon as

the current milliseconds count has expired.