Texas Instruments MSC1210 User Manual

Page 258

Interrupts

17-30

17.9 Interrupts

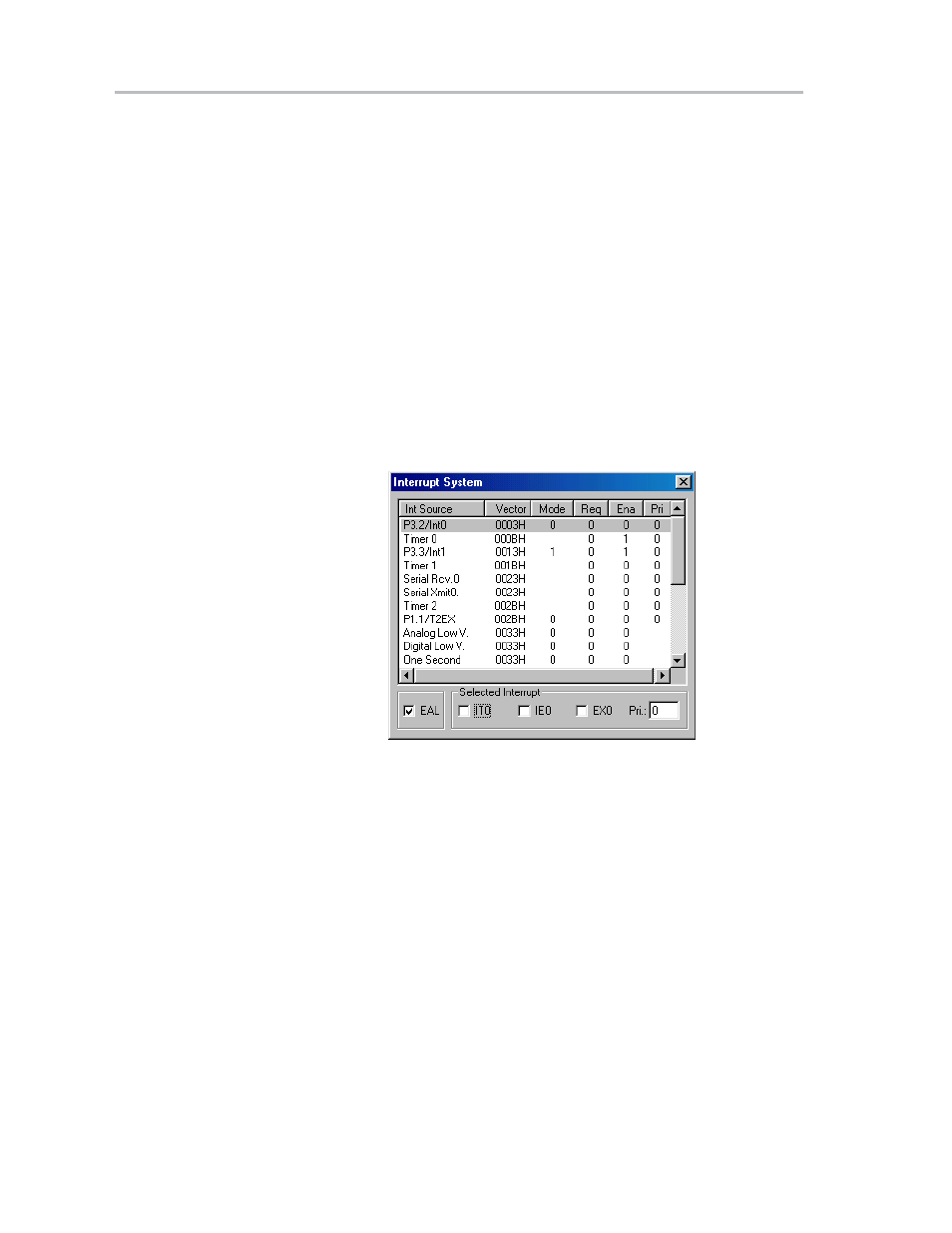

The list box for the interrupt peripheral is shown in Figure 17−13. The figure

shows a list of interrupt sources along with their associated vector addresses

that the processor automatically vectors to in the event that an enabled inter-

rupt is triggered, there are no pending interrupt requests of higher priority, and

there is no ISR being executed pertaining to an interrupt source of higher prior-

ity. As shown in Figure 17−13, the columns with headings Int Source, Vector,

Mode, Req, Ena and Pri pertain, respectively, to the interrupt source name, the

interrupt vector address, the interrupt edge type, (0 for level triggered and 1

for edge triggered), the interrupt request status, the interrupt enabled status

and its priority level. There are some interrupt sources listed without any prior-

ity listing. All such sources have the same vector address as that of the AI inter-

rupt. The priority levels of all interrupts affiliated with it are also unalterable and

have the highest priority level setting because the AI has the highest, and an

unalterable, priority.

Figure 17−13. List Box for the Interrupt Peripheral

Selecting any of the itemized interrupt sources will force its pertinent associated

settings and status value to be transferred to the set of check boxes in the lower

part of the Interrupt display. Clicking on its corresponding check box could alter

the status of each piece of information. On the Interrupt display shown in

Figure 17−13, the set of check boxes in the lower section of the display indicate

that the Global Enable flag EA is high (EA has a check). This implies that any in-

terrupt source that is enabled has the potential to generate an interrupt request.

If the EA button is clicked, clearing the selection, the processor’s interrupts are

globally disabled. Just for clarification, it should be restated that the status of EA

has no bearing on the ability of a AI interrupt condition, or those of any of the pe-

ripheral interrupts tied to it, to initiate an interrupt request. Setting the EFPI bit of

EICON enables the AI. One could induce an interrupt by placing a check on the

corresponding Req slot of the desired interrupt source. This is equivalent to acti-

vating the interrupt through the software or the hardware.

Sample routines of the interrupt peripheral module have been incorporated

into sample programs for other peripheral modules that have been discussed

previously. Please study those programs for more information.