Texas Instruments MSC1210 User Manual

Page 153

Summation/Shifter Register

12-17

Analog-to-Digital Converter

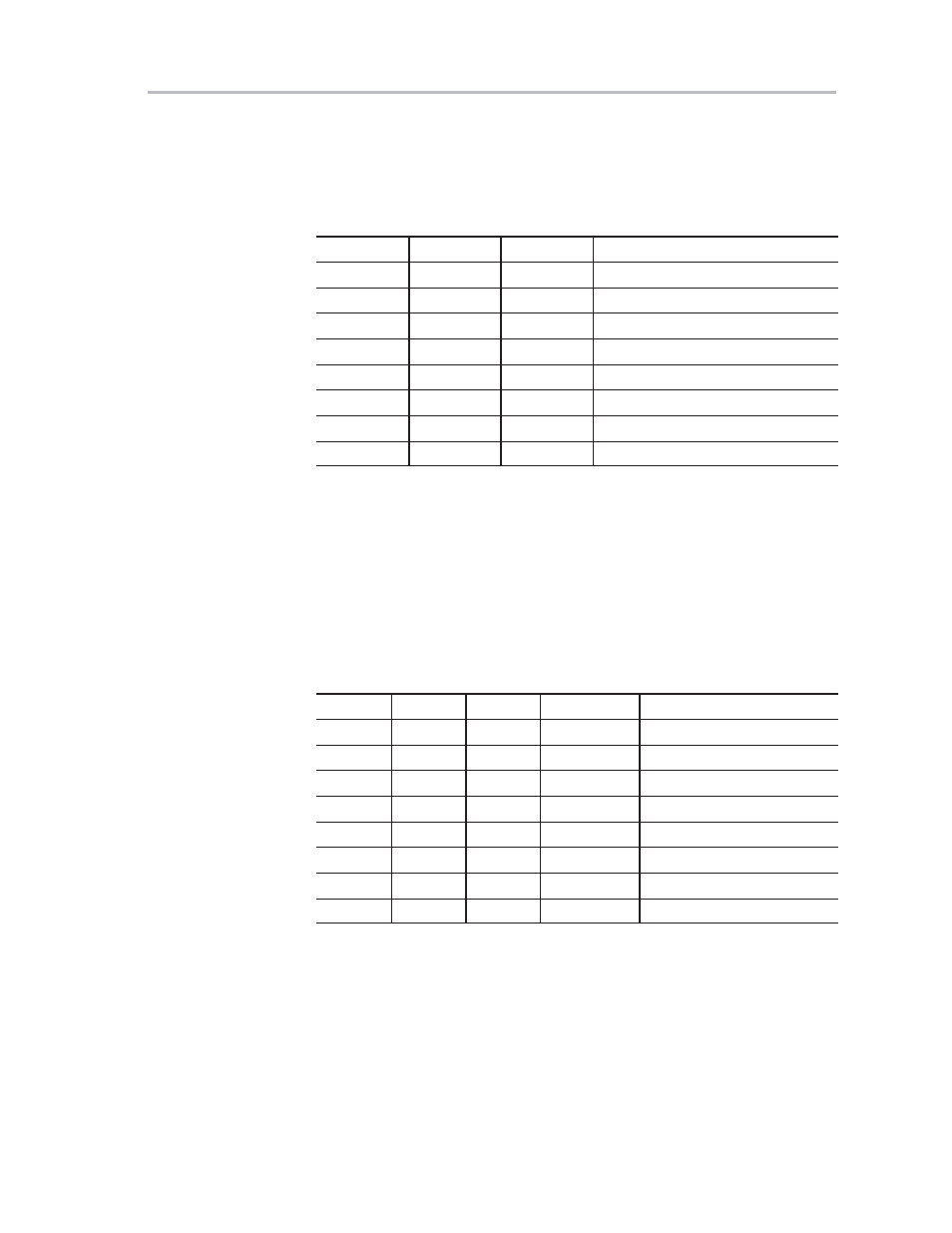

SSCON1 and SSCON0 (SSCON.7 and SSCON.6, respectively) control which

of the four modes the summation register will operate in.

SCNT0, SCNT1, and SCNT2 (SSCON.3 through SSCON.5) are used to indi-

cate how many ADC samples should be obtained and summed to the summa-

tion register. The number of samples that will be obtained and added are:

SCNT2

SCNT1

SCNT0

Summation Count

0

0

0

2

0

0

1

4

0

1

0

8

0

1

1

16

1

0

0

32

1

0

1

64

1

1

0

128

1

1

1

256

When the requested number of samples have been obtained and summed, a

summation auxiliary interrupt will be triggered, if enabled.

SHF2, SHF1, and SHF0 (SSCON.0 through SSCON.2) are used to indicate

by what value the final summation value should be divided. Specifically, the

value indicates how many bits to the right the final summation value will be

shifted, less one. Thus, a shift count of 0 reflects a final right shift by 1, which

equates to a divide by 2. A shift count of 4 reflects a final right shift by 5, which

equates to a divide by 32.

SHF2

SHF1

SHF0

Shift

Summation Count

0

0

0

1

2

0

0

1

2

4

0

1

0

3

8

0

1

1

4

16

1

0

0

5

32

1

0

1

6

64

1

1

0

7

128

1

1

1

8

256