2 events that can trigger interrupts, Table 10−1.interrupt sources – Texas Instruments MSC1210 User Manual

Page 109

Events That Can Trigger Interrupts

10-3

Interrupts

Thus, every 65 536 instruction cycles, Timer 0 overflows and the CPL and

RETI instructions are executed. Those two instructions together require three

instruction cycles, and accomplish the same goal as the first example. As far

as the toggling of P3.0 goes, the code is 437 times more efficient! Not to men-

tion it is much easier to read and understand because the timer 0 flag does not

have to be checked in the main program. Just setup the interrupt and forget

about it, secure in the knowledge that the MSC1210 will execute the code

whenever it is necessary.

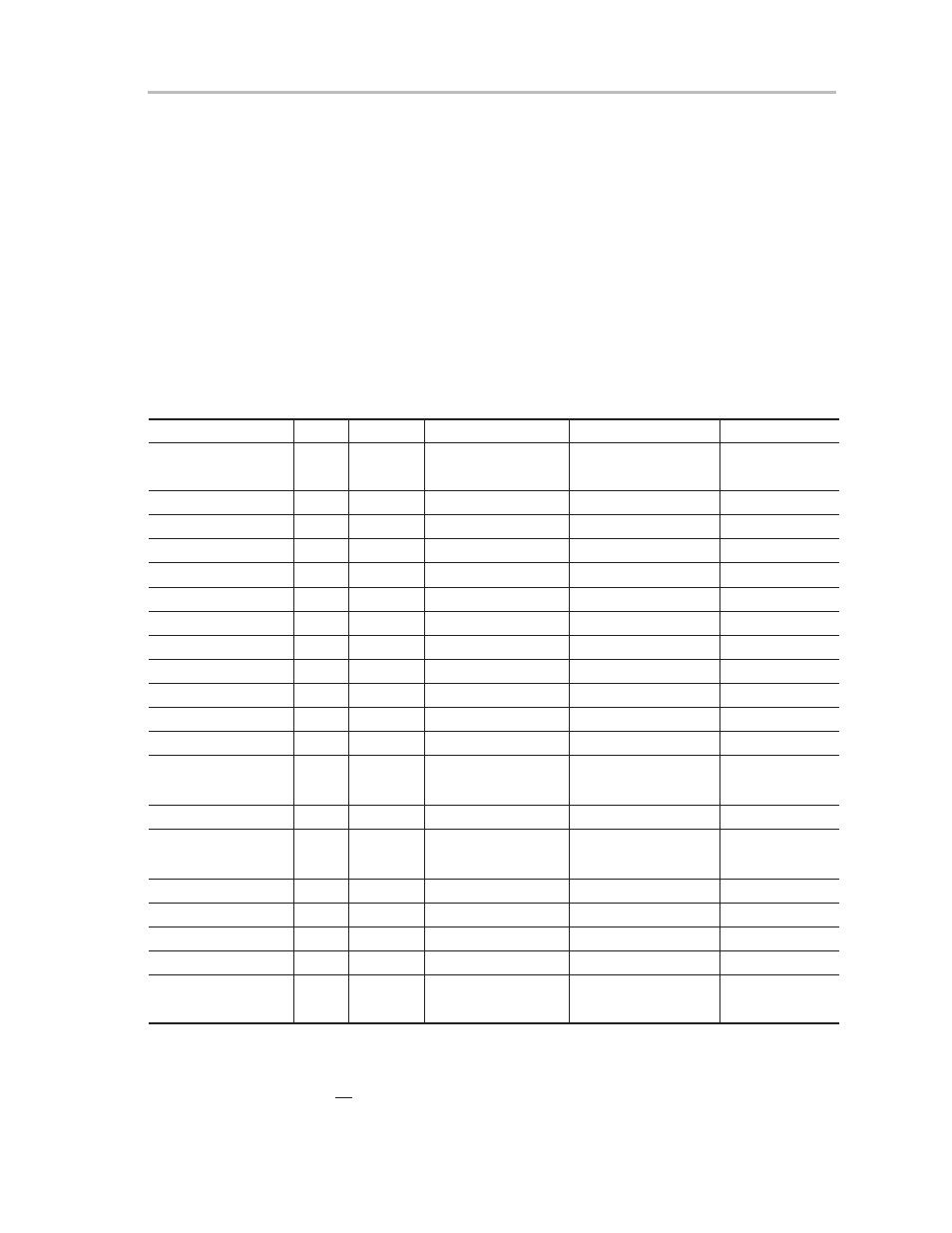

10.2 Events That Can Trigger Interrupts

The MSC1210 can be configured so that any of the events in Table 10−1 will

cause an interrupt.

Table 10−1.Interrupt Sources

Interrupt/Event

Addr

Priority

Flag

Enable

Priority Control

DV

DD

Low-Voltage

HW Breakpoint

33

H

HIGH

0

EDLVB (AIE.0)

(1)

EBP (BPCON.0)

(1)

EDLVV (AIE.0)

(1)

EBP (BPCON.0)

(1)

N/A

Av

DD

Low Voltage

33

H

0

EALV (AIE.1)

(1)

EALV (AIE.1)

(1)

N/A

SPI Receive

33

H

0

ESPIR (AIE.2)

(1)

ESPIR (AIE.2)

(1)

N/A

SPI Transmit

33

H

0

ESPIT (AIE.3)

(1)

ESPIT (AIE.3)

(1)

N/A

Milliseconds Timer

33

H

0

EMSEC (AIE.4)

(1)

EMSEC (AIE.4)

(1)

N/A

ADC

33

H

0

EADC (AIE.5)

(1)

EADC (AIE.5)

(1)

N/A

Summation Register

33

H

0

ESUM (AIE.6)

(1)

ESUM (AIE.6)

(1)

N/A

Seconds timer

33

H

0

ESEC (AIE.7)

(1)

ESEC (AIE.7)

(1)

N/A

External Interrupt 0

03

H

1

IE0 (TCON.1)

(2)

EX0 (IE.0)

(4)

PX0 (IP.0)

Timer 0 Overflow

0B

H

2

TF0 (TCON.5)

(3)

ET0 (IE.1)

(4)

PT0 (IP.1)

External Interrupt 1

13

H

3

IE1 (TCON.3)

(2)

EX1 (IE.2)

(4)

PX1 (IP.2)

Timer 1 Overflow

1B

H

4

TF1 (TCON.7)

(3)

ET1 (IE.3)

(4)

PT1 (IP.3)

Serial Port 0

23

H

5

RI_0 (SCON0.0)

TI_0 (SCON0.1)

ES0 (IE.4)

(4)

PS0 (IP.4)

Timer 2 Overflow

2B

H

6

TF2 (T2CON.7)

ET2 (IE.5)

(4)

PT2 (IP.5)

Serial Port 1

3B

H

7

RI_1 (SCON1.0)

TI_1 (SCON1.1)

ES1 (IE.6)

(4)

PS1 (IP.6)

External Interrupt 2

43

H

8

IE2 (EXIF.4)

EX2 (EIE.0)

(4)

PX2 (EIP.0)

External Interrupt 3

4B

H

9

IE3 (EXIF.5)

EX3 (EIE.1)

(4)

PX3 (EIP.1)

External Interrupt 4

53

H

10

IE4 (EXIF.6)

EX4 (EIE.2)

(4)

PX4 (EIP.2)

External Interrupt 5

5B

H

11

IE5 (EXIF.7)

EX5 (EIE.3)

(4)

PX5 (EIP.3)

Watchdog

63

H

12

LOW

WDTI (EICON.3)

EWDI (EIE.4)

(4)

PWDI (EIP.4)

Notes:

1) These interrupts set the AI flag (EICON.4) and are enabled by EAI (EICON.5).

2) If edge triggered, cleared automatically by hardware when the service routine is vectored to. If level triggered, the

flag follows the state of the pin.

3) Cleared automatically by hardware when interrupt vector occurs.

4) Globally enabled by EA (IE.7).