Texas Instruments MSC1210 User Manual

Page 29

Program Memory

2-3

MSC1210 Memory Organization

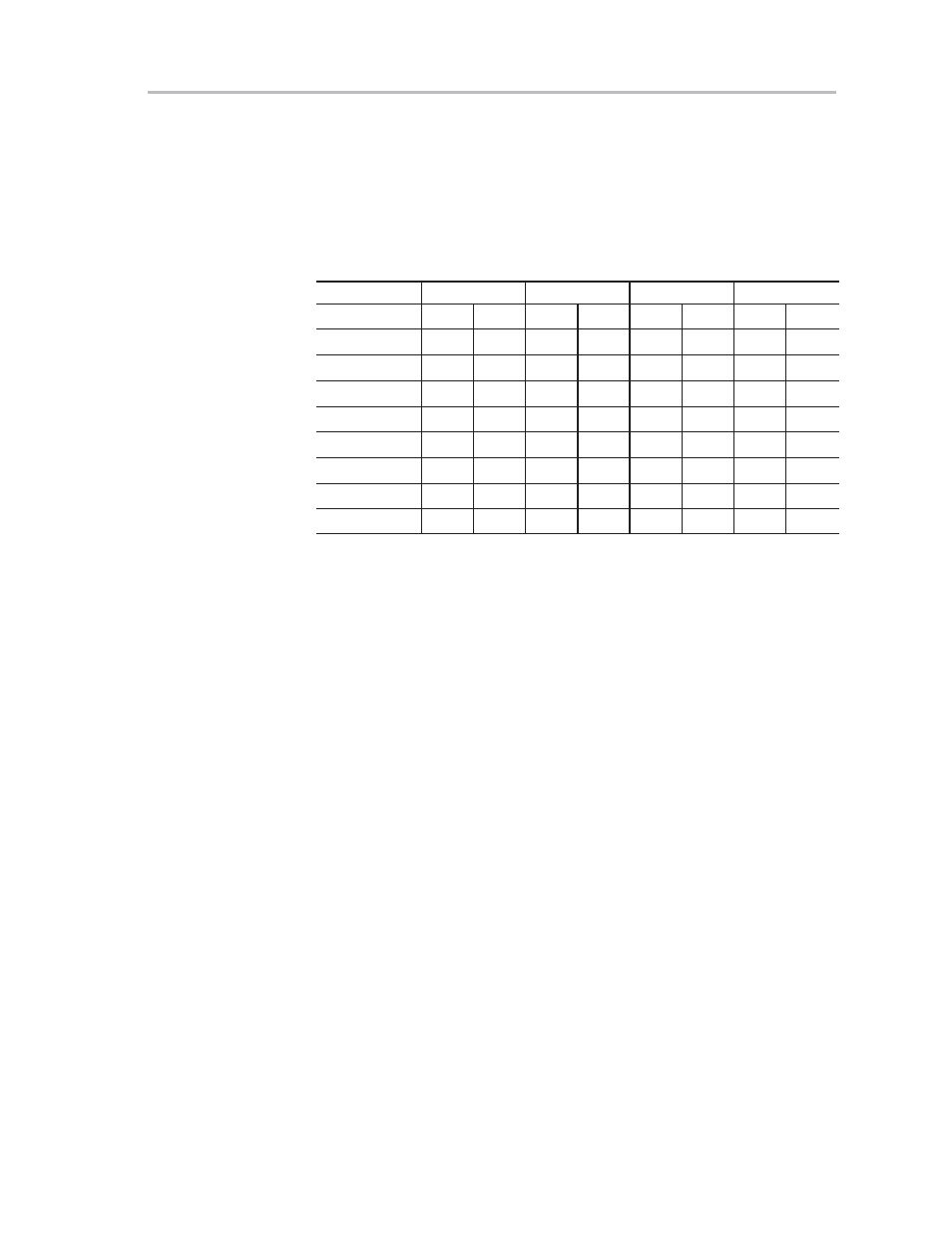

For example, in the Y5 model there is 32k flash memory available. This 32k

may be configured as either program memory, data memory, or both. This con-

figuration is set at the moment the firmware is loaded onto the MSC1210 by

setting hardware configuration register HCR0 as per Table 2−1. This table in-

dicates the total amount of program and data memory available for each part

revision given a specific HCR0 setting.

Table 2−1. Program and Data Memory Size.

HCR0

MSC1210Y2

MSC1210Y3

MSC1210Y4

MSC1210Y5

DFSEL

PM

DM

PM

DM

PM

DM

PM

DM

000

0kB

4kB

0kB

8kB

0kB

16kB

0kB

32kB

001

0kB

4kB

0kB

8kB

0kB

16kB

0kB

32kB

010

0kB

4kB

0kB

8kB

0kB

16kB

16kB

16kB

011

0kB

4kB

0kB

8kB

8kB

8kB

24kB

8kB

100

0kB

4kB

4kB

4kB

12kB

4kB

28kB

4kB

101

2kB

2kB

6kB

2kB

14kB

2kB

30kB

2kB

110

3kB

1kB

7kB

1kB

15kB

1kB

31kB

1kB

111 (default)

4kB

0kB

8kB

0kB

16kB

0kB

32kB

0kB

Note:

When a 0kB program memory configuration is selected, program execution is external

For example, setting the DFSEL bits to 110 with a MSC1210Y5 would cause

31kb of on-chip flash memory to be partitioned as program memory and 1kb

of flash memory to be partitioned as data memory.

Table 2−2 indicates where the assigned memory will be located in address

space. This table provides essentially the same information as Table 2−1, but

also indicates where the memory will be located. For example, the DFSEL =

110 example in the previous paragraph (31kb of on-chip flash program

memory, 1k of on-chip flash data memory) appears in Table 2−2 as flash pro-

gram memory from 0000

H

to 7BFF

H

(which is 31k) and flash data memory from

0400

H

to 07FF

H

(which is 1k).

Note that the Data memory address starts at 0400

H

because the first 1k

(0000

H

-03FF

H

) is, by default, used to address the on-chip extended SRAM.

The location of on-chip extended SRAM may be changed by using the Memory

Control (MCON) SFR. By setting bit 0 of MCON, the on-chip extended SRAM

may be moved from 0000

H

-03FF

H

to 8400

H

-87FF

H

. However, on-chip ex-

tended flash data memory always begins at 0400

H

regardless of whether or

not SRAM is located at 0000

H

or 8400

H

.