Texas Instruments MSC1210 User Manual

Page 178

Watchdog Timer

14-4

14.3 Watchdog Timer

The watchdog timer is used to ensure that the CPU is executing the user

program and not some random sequence of instructions provoked by a

malfunction. When the watchdog timer is enabled, the user program must

periodically notify the watchdog that the program is still running correctly. If the

watchdog detects that the user program has not made this notification after a

certain amount of time, the watchdog automatically resets the MCS1210 or

executes an interrupt. This ensures that the part does not hang in an infinite loop

or execute non-program code due to some malfunction or programming error.

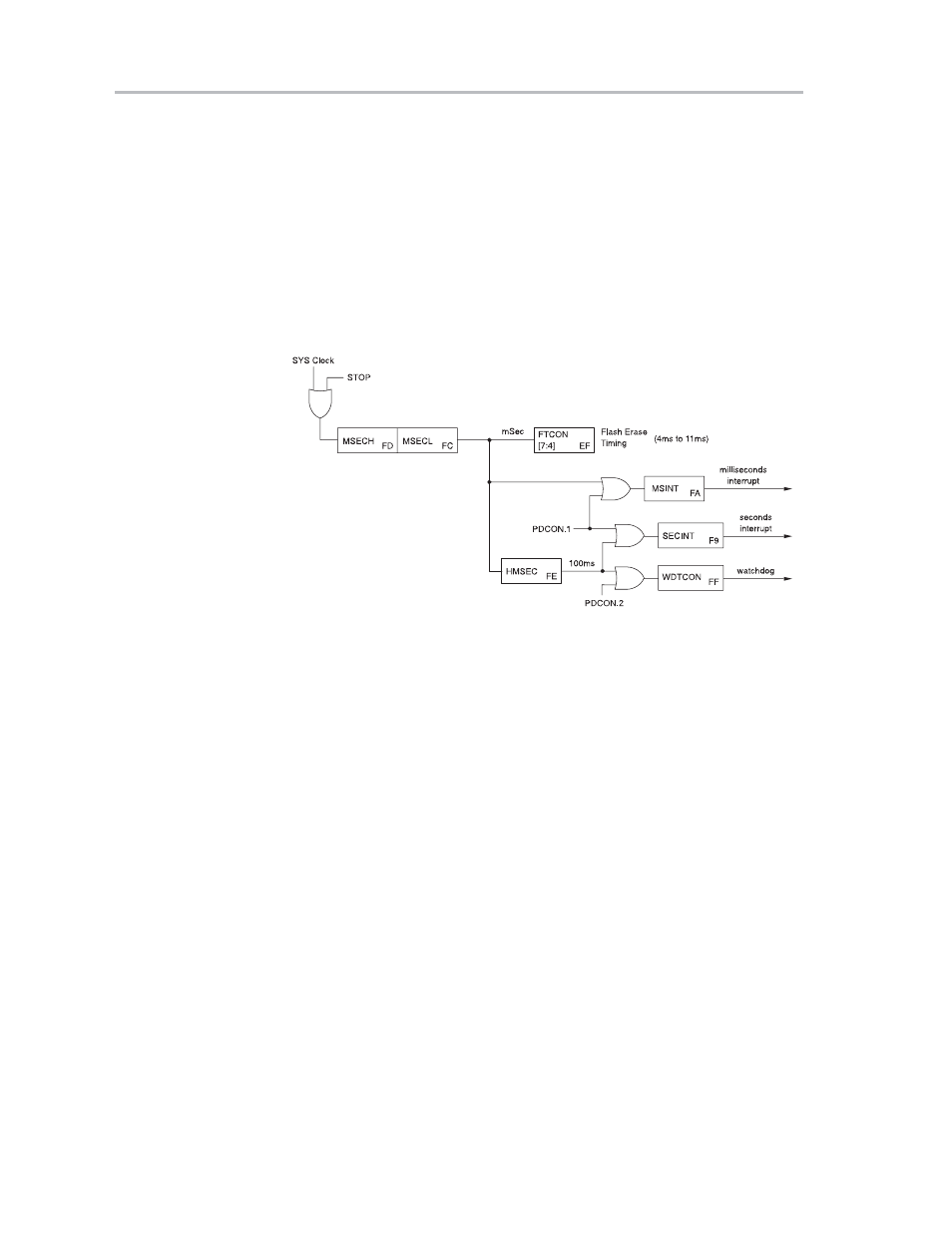

Figure 14−2. System Timing Interrupt Control

14.3.1 Watchdog Timer Hardware Configuration

The watchdog is first configured when code is downloaded to the MSC1210.

Bit 3 of hardware configuration register 0 (HCR0) is the Enable Watchdog

Reset (EWDR) bit. If this bit is set, the watchdog will trigger a reset (if the

watchdog is enabled by software and not reset at appropriate intervals),

whereas if this bit is clear, the watchdog will trigger an interrupt (if the watchdog

is enabled by software not reset at appropriate intervals). The point to

remember is that the EWDR bit in the HCR0 register indicates what the

watchdog will do when it is triggered: reset the MSC1210 or cause an interrupt.

It does not, by itself, enable or disable the watchdog; that is done in software

at execution time.