13 summation/shifter register – Texas Instruments MSC1210 User Manual

Page 152

Summation/Shifter Register

12-16

12.13 Summation/Shifter Register

The MSC1210 includes a summation/shifter register that facilitates and in-

creases the efficiency of certain common summation and shifting/division func-

tions, especially those related to ADC conversions. The summation register is

only active when the ADC is powered up. It is a 32-bit value that is broken into

four 8-bit SFRs named SUMR0 (LSB), SUMR1, SUMR2, and SUMR3 (MSB).

The summation registers may function in one of four distinct modes:

Manual Summation—values written manually to the summation registers will

be summed to the current sum (mode 0).

ADC Summation—a specified number of values returned by the ADC will au-

tomatically be summed to the current sum (mode 1).

Manual Shift/Divide—the current 32-bit value in the summation register is divid-

ed by a specified number. This division takes only four system cycles (mode 2).

ADC Summation with Shift/Divide—a specified number of values returned

by the ADC will automatically be summed to the current sum, then divided by

a specified number (mode 3).

The operation of the summation registers is controlled and configured with the

SSCON (E1

H

) SFR. In addition to controlling the four modes of operation,

SSCON also is used to control how many samples will be taken from the ADC

and by what value the final sum should be divided by, if any.

The individual bits of SSCON have the following functions:

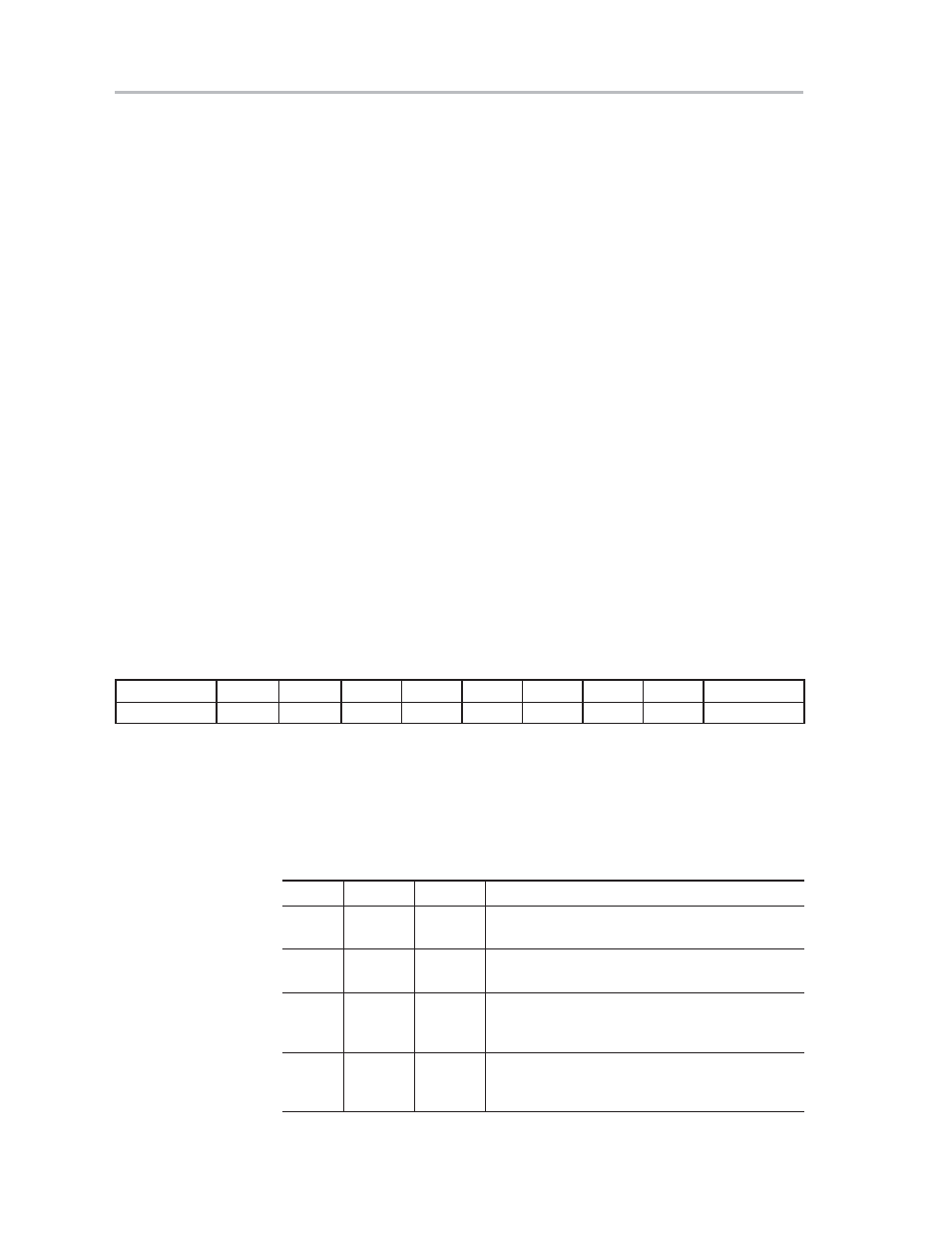

7

6

5

4

3

2

1

0

Reset Value

SFR E1H

SSCON1

SSCON0

SCNT2

SCNT1

SCNT0

SHF2

SHF1

SHF0

00H

The summation register is powered down when the ADC is powered down. If

all zeroes are written to this register, the 32-bit SUMR3-0 registers will be

cleared. The summation registers will do sign extend if bipolar is selected in

ADCON1.

SSCON1-0 (bits 7-6)—Summation Shift Control.

Source

SSCON1

SSCON0 Mode

ADC

0

0

Values written to the SUM registers are accumu-

lated when the SUMR0 value is written.

CPU

0

1

Summation register enabled. Source is ADC,

summation count is working.

ADC

1

0

Shift enabled. Summation register is shifted by

SHF Count bits. It takes four system clocks to

execute.

CPU

1

1

Accumulate and shift enabled. Values are accu-

mulated for SUM count times and then shifted by

SHF count.