3 pwm generator – Texas Instruments MSC1210 User Manual

Page 129

PWM Generator

11-5

Pulse Width Modulator/Tone Generator

11.3 PWM Generator

The PWM generator is activated when TPCNTL[1:0] = 01. This setting allows

a PWM waveform to be generated automatically by the MSC1210 with charac-

teristics defined by the user program. The PWM is configured based on the

PWMCON SFR, the PWM Period and PWM Duty settings, and the USEC SFR

setting. The USEC SFR or SYS clock (defined by Speed Select) generates a

tick that defines the unit period that is used by PWM Period and PWM Duty in

defining the waveform.

As its name indicates, the PWM Period register gives us the period of the PWM

wave, whereas the PWM Duty register defines the length of time which sets

the duty cycle. We can program either the ON duty or the OFF duty depending

on the bit PPOL (PWMCOM.5). If PPOL is set, then OFF duty period is pro-

grammed, and if it cleared, then ON duty period is programmed. The duty cycle

is periodic with respect to the period of PWM, irrespective of the duty register.

The duty cycle of the PWM wave for different configurations is shown in the

following equations and in Table 11−1.

WhenPPOL (PWMCON.5) = 0:

PWM Frequency = 1/T

BASE

S

(PWM Period[15:0] + 1)

PWM ON Period = T

BASE

S

PWM Duty[15:0]

Duty Cycle = PWM Duty/(PWM Period[15:0] +1)

Where:

T

BASE

= T

CLK

when SPDSEL = 1,

T

BASE

= T

USEC

when SPDSEL = 0.

WhenPPOL (PWMCON.5) = 1, PWM Duty is controlling the OFF period, there-

fore:

Duty Cycle = PWM Period +1 − PWM Duty/PWM Period +1.

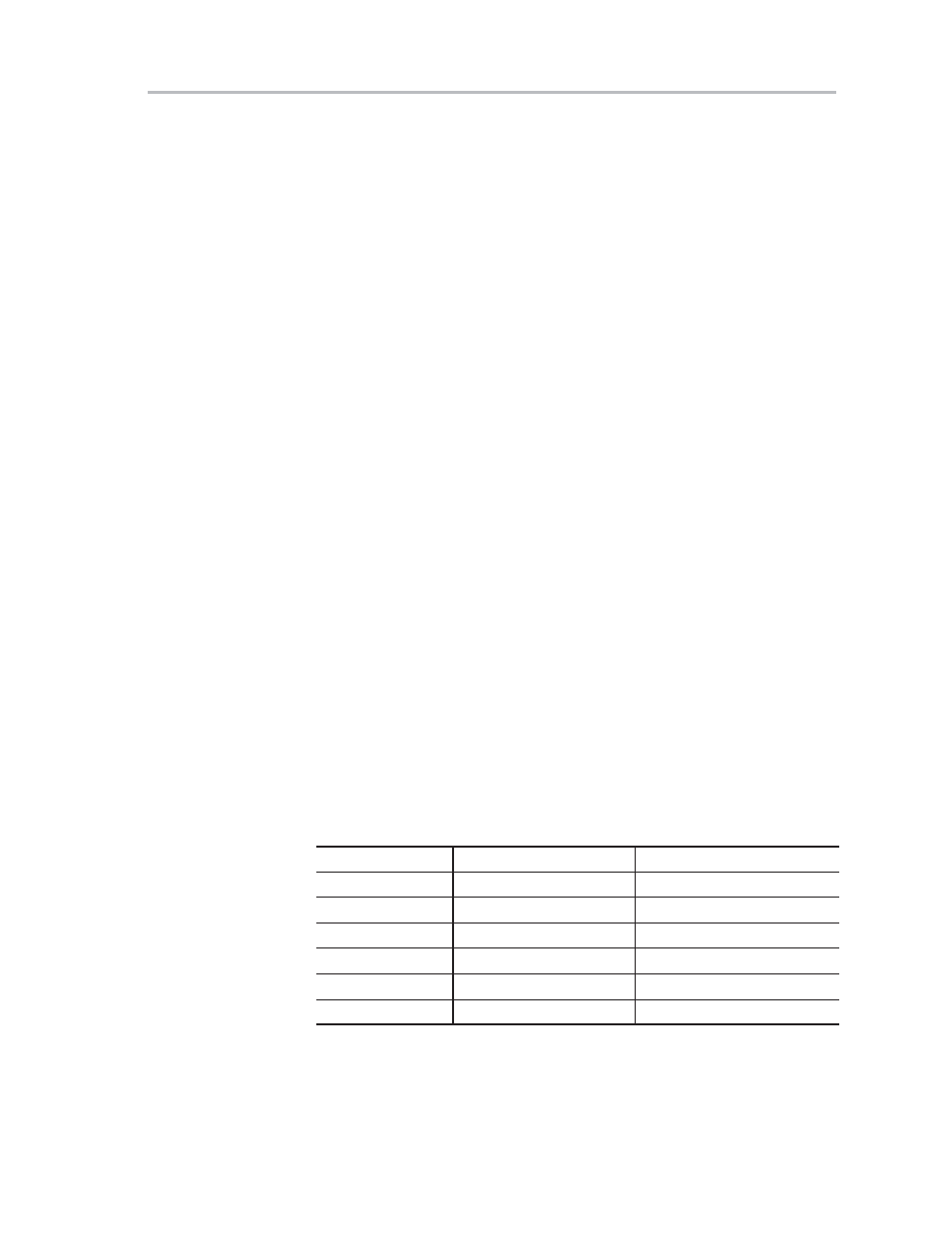

Table 11−1. PWM Polarity Conditions

PPOL

Condition

Duty Cycle

0

Period = X, Duty = 0

0% (always outputs low)

0

0 < Duty

≤

Period

Intermediate Value

0

Duty > Period

100% (always outputs high)

1

Period = X, Duty = 0

100% (logic

‘

1’)

1

0 < Duty

≤

Period

Intermediate Value

1

Duty > Period

0% (logic

‘0

’)