Texas Instruments MSC1210 User Manual

Page 116

Types of Interrupts

10-10

Note:

Level-sensitive interrupts are not latched. If the interrupt is level-sensitive,

the condition must be present until the processor can respond to it. This is

most important if other interrupts are being used with a higher or equal prior-

ity. If the device is currently processing another interrupt of higher priority, the

condition must be present until the current interrupt is complete. This is be-

cause the level-sensitive interrupt is not sampled until the RETI instruction

is executed. Upon returning, if the level-triggered interrupting signal is not

there, it is as though the interrupt request was never issued.

The remaining four external interrupts are similar in nature, with one differ-

ence: INT2 and INT4 are positive edge detect only, while INT3 and INT5 are

negative edge detect only. These interrupts do not have level-detect modes.

All associated bits and flags operate the same and have the same polarity as

the first two interrupts. A logic 1 on an interrupt flag indicates the presence of

an interrupt condition, not the logic state of the input pin.

The flags that trigger external interrupts 2 through 5 are found in the EXIF (91

H

)

SFR, as shown in Table 10−7. When the appropriate condition (falling-edge

or rising-edge) is detected, the corresponding flag is set and the interrupt is

triggered, if enabled.

Note:

The bits in EXIF are set to 1 to indicate that the condition is true—the bits do

not represent the current level of the pin. That is, IE5 will be set to 1 when

a falling edge is detected on INT5, even though INT5 is at a logic 0 level at

that point.

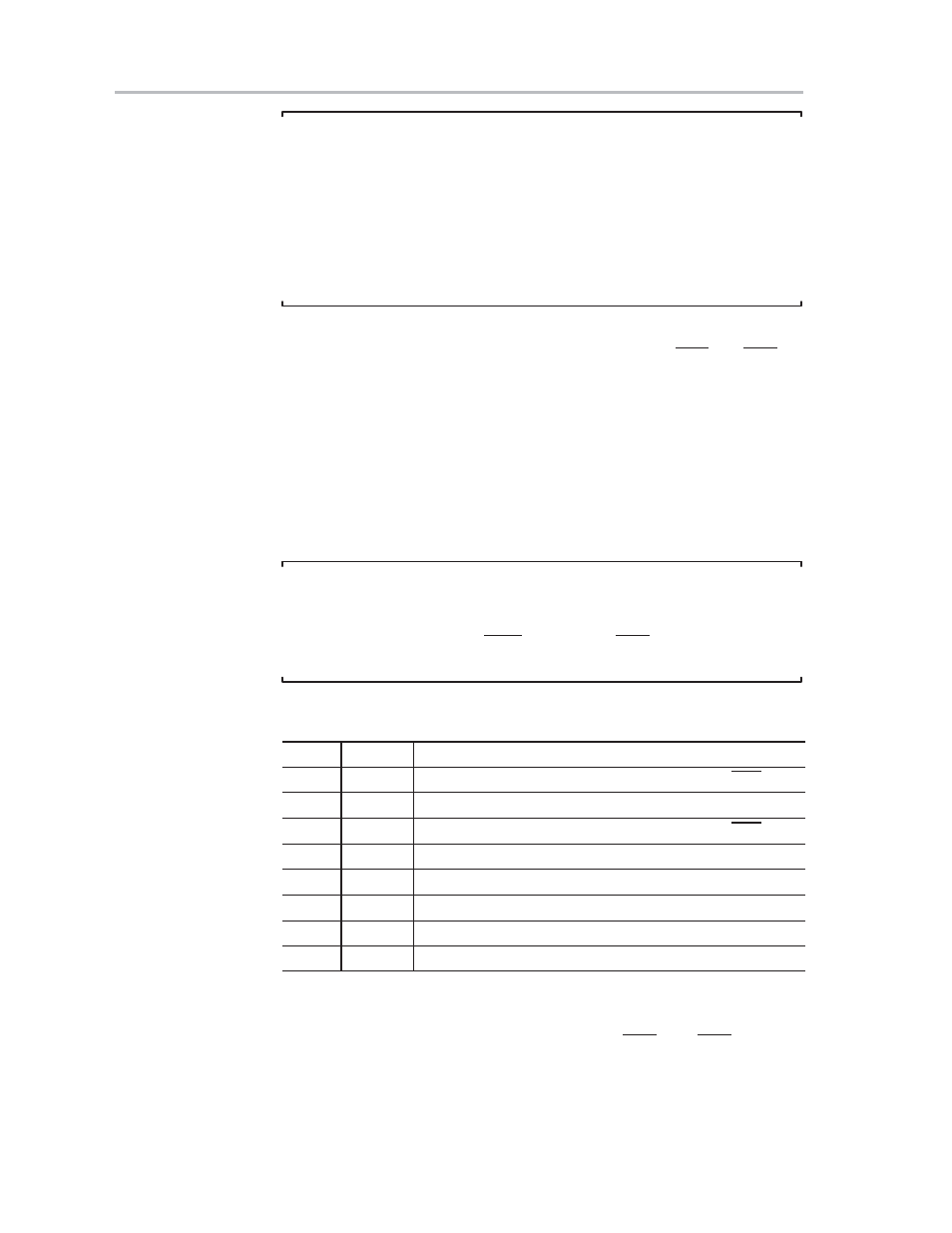

Table 10−7.EXIF (91

H

) SFR

Bit

Name

Explanation of Function

7

IE5

External interrupt 5 flag – falling edge detected on INT5

6

IE4

External interrupt 4 flag – rising edge detected on INT4

5

IE3

External interrupt 3 flag – falling edge detected on INT3

4

IE2

External interrupt 2 flag – rising edge detected on INT2

3

−

Reserved (cleared to 1)

2

−

Undefined (cleared to 0)

1

−

Undefined (cleared to 0)

0

−

Undefined (cleared to 0)

There are three interrupts that can wake up the processor if it is in the

low-power IDLE mode: the external interrupts (INT0 and INT1), and the

Watchdog (when used as an interrupt). In order to be used to wake up the

processor, they must be enabled in the Wake Up Enable register, WUEN

(C6

H

).