Timer 2 control (t2con) – Texas Instruments MSC1210 User Manual

Page 320

Bit Addressable SFRs (alphabetical)

F-10

Timer 2 Control (T2CON)

SFR Name:

T2CON

SFR Address:

C8

H

Bit−Addressable: Yes

Bit−Definitions:

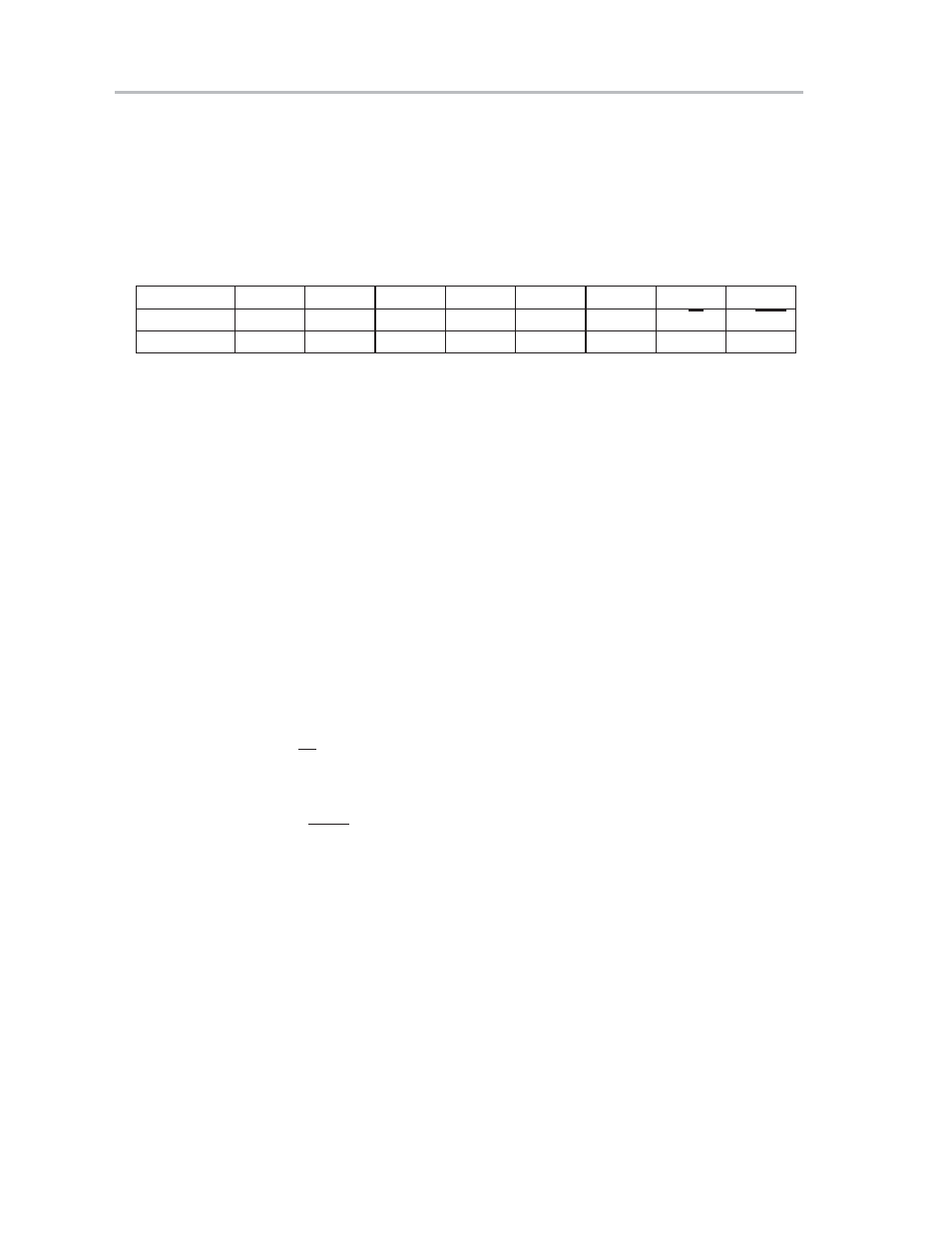

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

Name

TF2

EXF2

RCLK

TCLK

EXEN2

TR2

C/T2

CP/RL2C

Bit Address

CFH

CEH

CDH

CCH

CBH

CAH

C9H

C8H

TF2—Timer 2 Overflow Flag. This bit is set by the MCU when Timer 2 over-

flows from FFFF

H

back to 0000

H

. When enabled, this bit causes a Timer 2 in-

terrupt. Cleared by software. This bit is not set when TCLK or RCLK is set.

EXF—Timer 2 External Flag. This bit is set by the MCU when a timer capture

or reload is triggered by a 1-0 transition on T2EX. When enabled, this bit

causes a Timer 2 interrupt. Cleared by software.

RCLK—Timer 2 Receive Clock. When this bit is set, Timer 2 provides the se-

rial port receive baud rate clock.

TCLK—Timer 2 Transmit Clock. When this bit is set, Timer 2 provides the

serial port transmit baud rate clock.

EXEN2—Timer 2 External Enable. When this bit is set, a capture or reload

is triggered on a 1-0 transition on the T2EX line.

TR2—Timer 2 Run Control. When this bit is set, Timer 2 is activated/run.

When this bit is clear, Timer 2 is stopped.

C/T2—Counter/Interval Timer. When this bit is set, Timer 2 acts as an event

counter based on external stimulus on the T2EX line. When this bit is clear,

Timer 2 acts as an interval timer.

CP/RL2C—Capture/Reload. When set, a capture occurs on a 1-0 transition

of T2EX. When clear, a reload occurs on timer overflow or on a 1-0 transition

of T2EX. This bit is only relevant if EXEN2 is set, and does not apply if RCLK

or TCLK are set.