4 pi update, Flex-muxonenand4g(kfm4gh6q4m-debx) – Samsung FLEX-MUXONENAND KFN8GH6Q4M User Manual

Page 90

Flex-MuxOneNAND4G(KFM4GH6Q4M-DEBx)

- 90 -

FLASH MEMORY

Flex-MuxOneNAND8G(KFN8GH6Q4M-DEBx)

Flex-MuxOneNAND16G(KFKAGH6Q4M-DEBx)

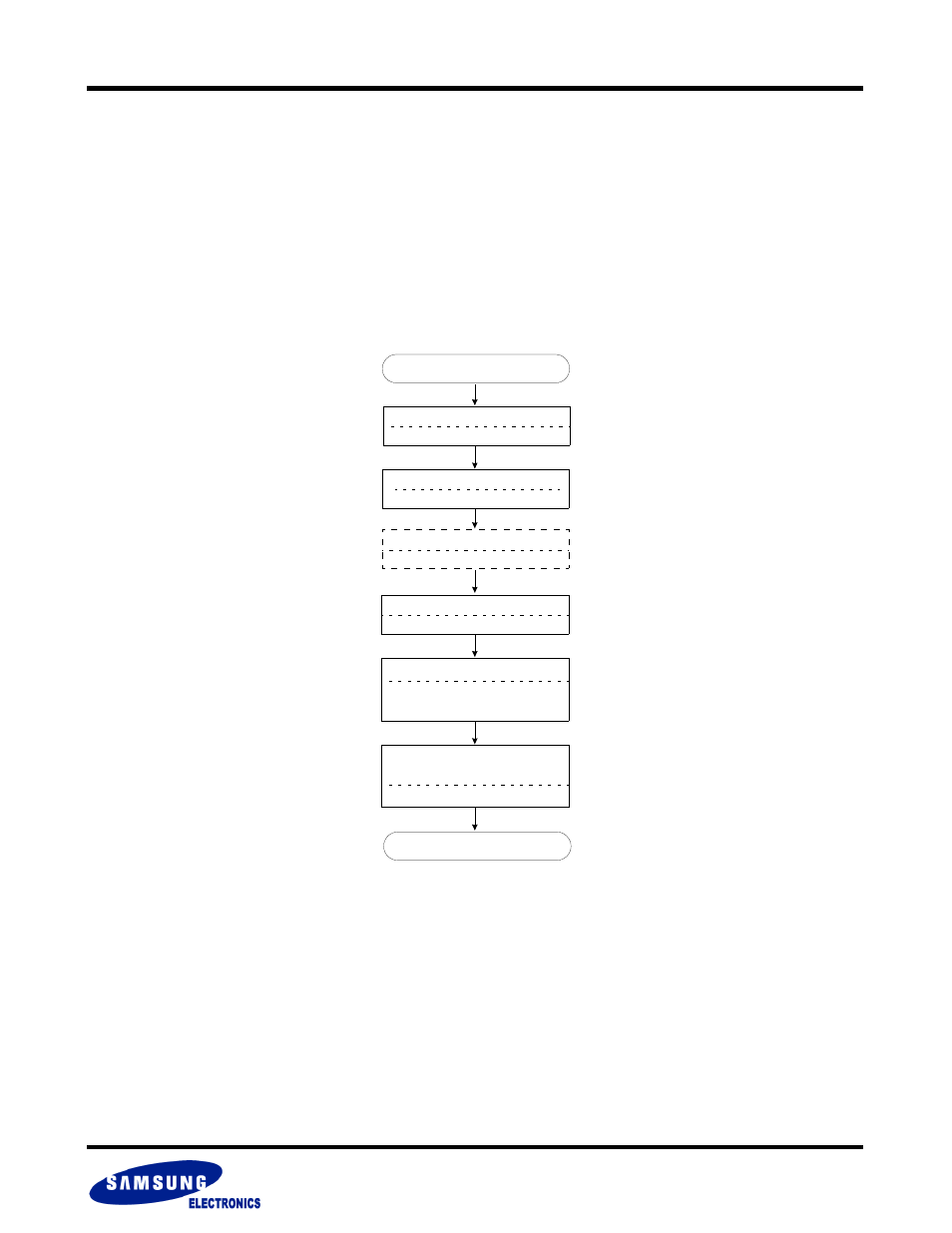

3.12.1.4 PI Update

Once new partition information is programmed into the PI block, an internal register that is invisible to users must be updated for the changes

in PI to be applied. This internal register which stores partition information(i.e. the last address of SLC area and lock bits) will be automatically

updated through cold reset. However, the internal register can also be updated by issuing Partition Information Update command(05h) after PI

Access mode entry.

Update the PI Area

• Issue the PI Access mode(Refer to Chapter 3.12.1.1).

• Issue the update PI command.

PI Block Update (In PI Block Access Mode)

NOTE :

1) FBA(NAND Flash Block Address) must be 0000h.

2) BSA must be 1000 and BSC must be 000.

3) ‘Write 0 to interrupt register’ step may be ignored when using INT auto mode. Refer to chapter 2.8.18.1

4) FPA must be 00h and FSA must be 00.

Start

Write Update PI command

DQ=0005h

Wait for INT register

low to high transition

Add: F241h DQ[15]=INT

Add: F220h

PI updated

Write 0 to interrupt register

3)

Add: F241h DQ=0000h

Write ‘DFS, FBA’ of Flash

1)

Add: F100h DQ=DFS, FBA

* DBS, DFS is for DDP

Write ‘BSA, BSC’ of DataRAM

Add: F200h DQ=0800h

2)

Write ‘FPA, FSA’ of Flash

Add: F107h DQ=0000h

4)