5 block diagram, 6 memory array organization, 1 internal (nand array) memory organization – Samsung FLEX-MUXONENAND KFN8GH6Q4M User Manual

Page 11: Flex-muxonenand4g(kfm4gh6q4m-debx)

Flex-MuxOneNAND4G(KFM4GH6Q4M-DEBx)

- 11 -

FLASH MEMORY

Flex-MuxOneNAND8G(KFN8GH6Q4M-DEBx)

Flex-MuxOneNAND16G(KFKAGH6Q4M-DEBx)

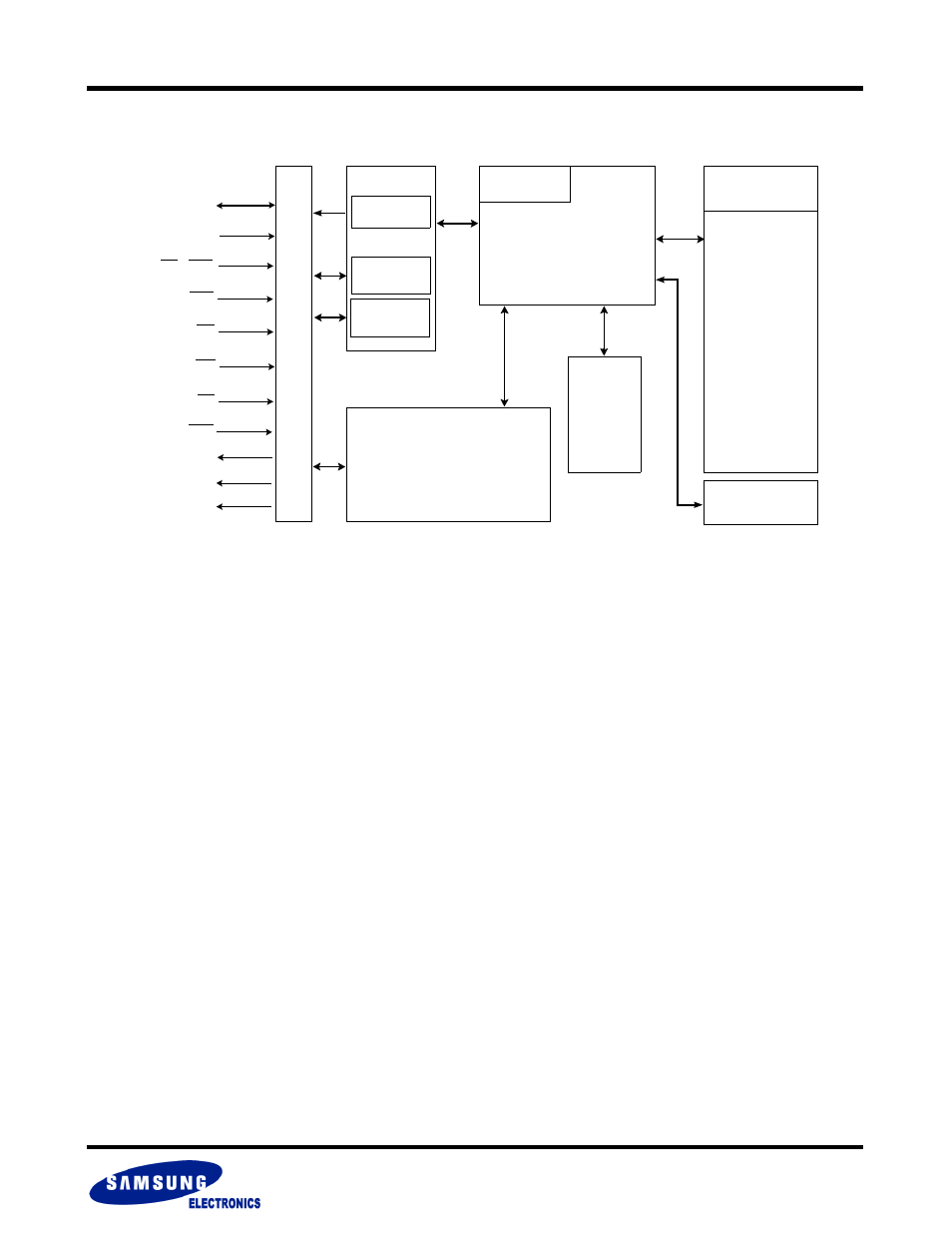

2.5 Block Diagram

2.6 Memory Array Organization

The Flex-MuxOneNAND architecture integrates several memory areas on a single chip.

2.6.1 Internal (NAND Array) Memory Organization

The on-chip internal memory is a convertible(SLC and MLC) NAND array used for data storage and code. The internal memory is divided into

a main area and a spare area.

Main Area

The main area is the primary memory array. A block incorporates 64pages(SLC) or 128pages(MLC). A main page size is 4KB and a main

page is comprised of 8 sectors each size of which is 512Byte.

Spare Area

The spare area is used for invalid block information and ECC storage. Spare area internal memory is associated with corresponding main area

memory. A spare page size is 128B and a spare page is comprised of 8 sectors each size of which is 16Byte.

BootRAM

StateMachine

Bootloader

Internal Registers

(Address/Command/Configuration

/Status Registers)

Error

Correction

Logic

DataRAM0

BufferRAM

NAND Flash

Array

OTP

(One Block)

DataRAM1

1st Block OTP

H

o

st Interf

ace

CLK

OE

WE

RP

AVD

INT/INT1

RDY

ADQ15~ADQ0

CE2

CE / CE1

(Block 0)

INT2