2 polling the interrupt register status bit, Flex-muxonenand4g(kfm4gh6q4m-debx) – Samsung FLEX-MUXONENAND KFN8GH6Q4M User Manual

Page 134

Flex-MuxOneNAND4G(KFM4GH6Q4M-DEBx)

- 134 -

FLASH MEMORY

Flex-MuxOneNAND8G(KFN8GH6Q4M-DEBx)

Flex-MuxOneNAND16G(KFKAGH6Q4M-DEBx)

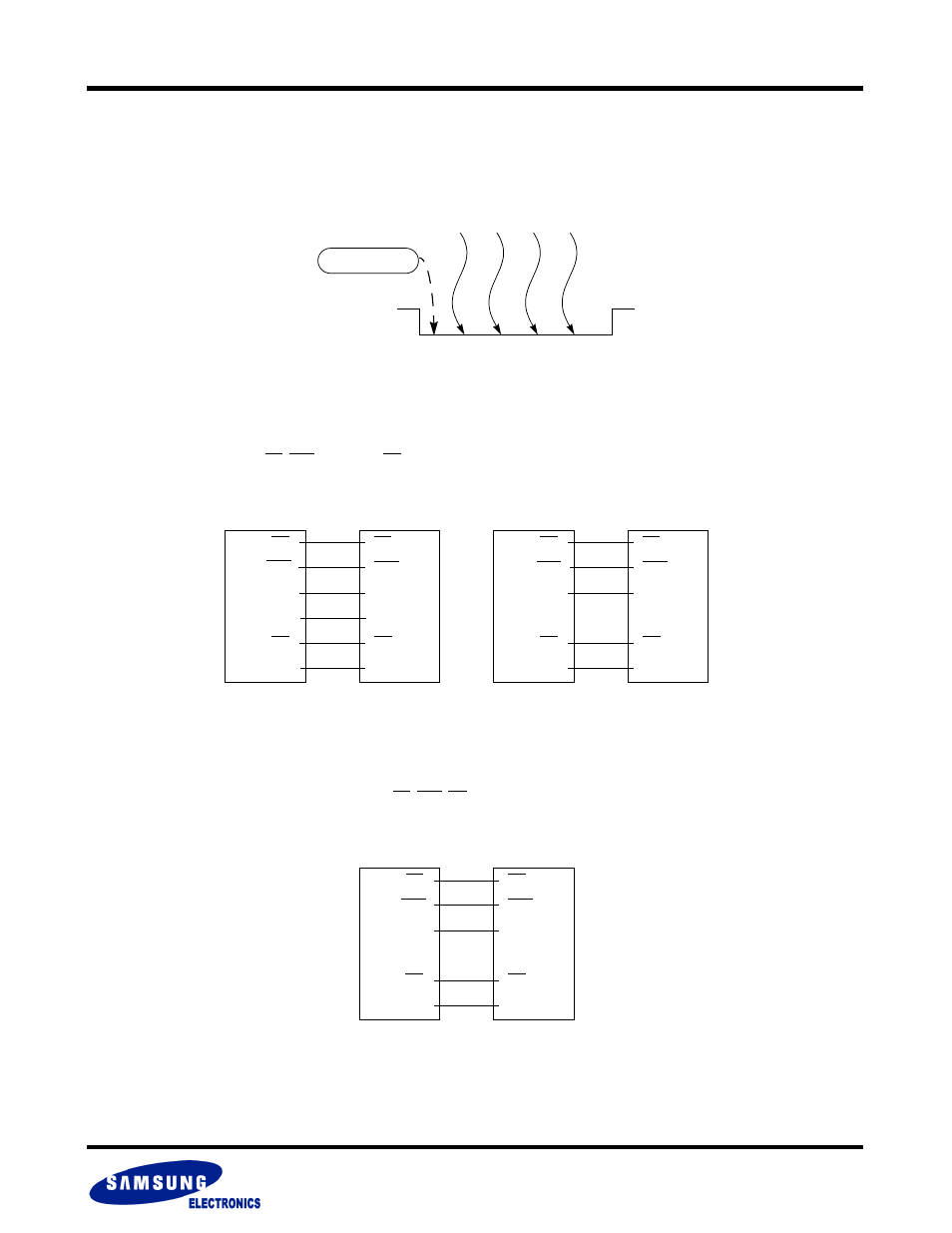

7.1.2 Polling the Interrupt Register Status Bit

An alternate method of determining the end of an operation is to continuously monitor the Interrupt Status Register Bit instead of using the INT

pin.

When using interrupt register instead of INT pin, INT must be unconnected

.

This can be configured in either a synchronous mode or an asynchronous mode.

Synchronous Mode Using Interrupt Status Register Bit Polling

When operating synchronously, CE, AVD, CLK, RDY, OE, and DQ pins on the host and Flex-MuxOneNAND are tied together.

RDY could be connected as one of following guides.

Asynchronous Mode Using Interrupt Status Register Bit Polling

When configured to operate in an asynchronous mode, CE, AVD, OE and DQ of the Flex-MuxOneNAND are tied to corresponding pins of the

Host. CLK is tied to the Host Vss (Ground). RDY is NOT connected.

INT

Command

Host

Flex-MuxOneNAND

RDY(WAIT)

OE

CLK

CE

RDY

OE

CLK

CE

AVD

DQ

DQ

Host

Flex-MuxOneNAND

OE

CLK

CE

RDY

OE

CLK

CE

AVD

DQ

DQ

Handshaking Mode

Non-Handshaking Mode

AVD

AVD

Host

Flex-MuxOneNAND

OE

CE

RDY

OE

CLK

CE

AVD

DQ

DQ

Vss

AVD