15 ecc operation, 1 ecc bypass operation, Flex-muxonenand4g(kfm4gh6q4m-debx) – Samsung FLEX-MUXONENAND KFN8GH6Q4M User Manual

Page 104

Flex-MuxOneNAND4G(KFM4GH6Q4M-DEBx)

- 104 -

FLASH MEMORY

Flex-MuxOneNAND8G(KFN8GH6Q4M-DEBx)

Flex-MuxOneNAND16G(KFKAGH6Q4M-DEBx)

3.15 ECC Operation

The Flex-MuxOneNAND device has on-chip ECC with the capability of correcting up to 4-bit errors in the NAND Flash Array memory main and

spare areas (512+16)B.

As the device transfers data from a BufferRAM to the NAND Flash Array memory Page Buffer for Program Operation, the device initiates a

background operation which generates an Error Correction Code (ECC).

During a Load operation from the NAND Flash Array memory Page, the on-chip ECC engine generates a new ECC. The 'Load ECC result' is

compared to the originally programmed ECC' thus detecting the number of errors. Up to 4-bit errors are corrected.

ECC is updated by the device automatically. After a Load Operation, the Host can determine whether there was error by reading the 'ECC Sta-

tus Register' (Refer to section 2.8.26~2.8.29).

Error types are divided into 'no error', 'correctable error(1bit~4bit)', and 'uncorrectable error(more than 4bit)'.

When the device reads the NAND Flash Array memory main and spare area data with an ECC operation, the device doesn't place the newly

generated ECC for main and spare area into the buffer. Instead it places the ECC which was generated and written during the program oper-

ation into the buffer.

An ECC operation is also done during the Boot Loading operation.

3.15.1 ECC Bypass Operation

In an ECC bypass operation, the device does not generate ECC as a background operation.

In a Program Operation the ECC code to NAND Flash Array memory spare area is not updated.

During a Load operation, the on-chip ECC engine does not generate a new ECC internally. Also the ECC Status Registers are invalid. The

error is not corrected and detected by itself, so that ECC bypass operation is not recommended for host.

ECC bypass operation is set by the 9bit of System Configuration 1 Register (see section 2.8.19)

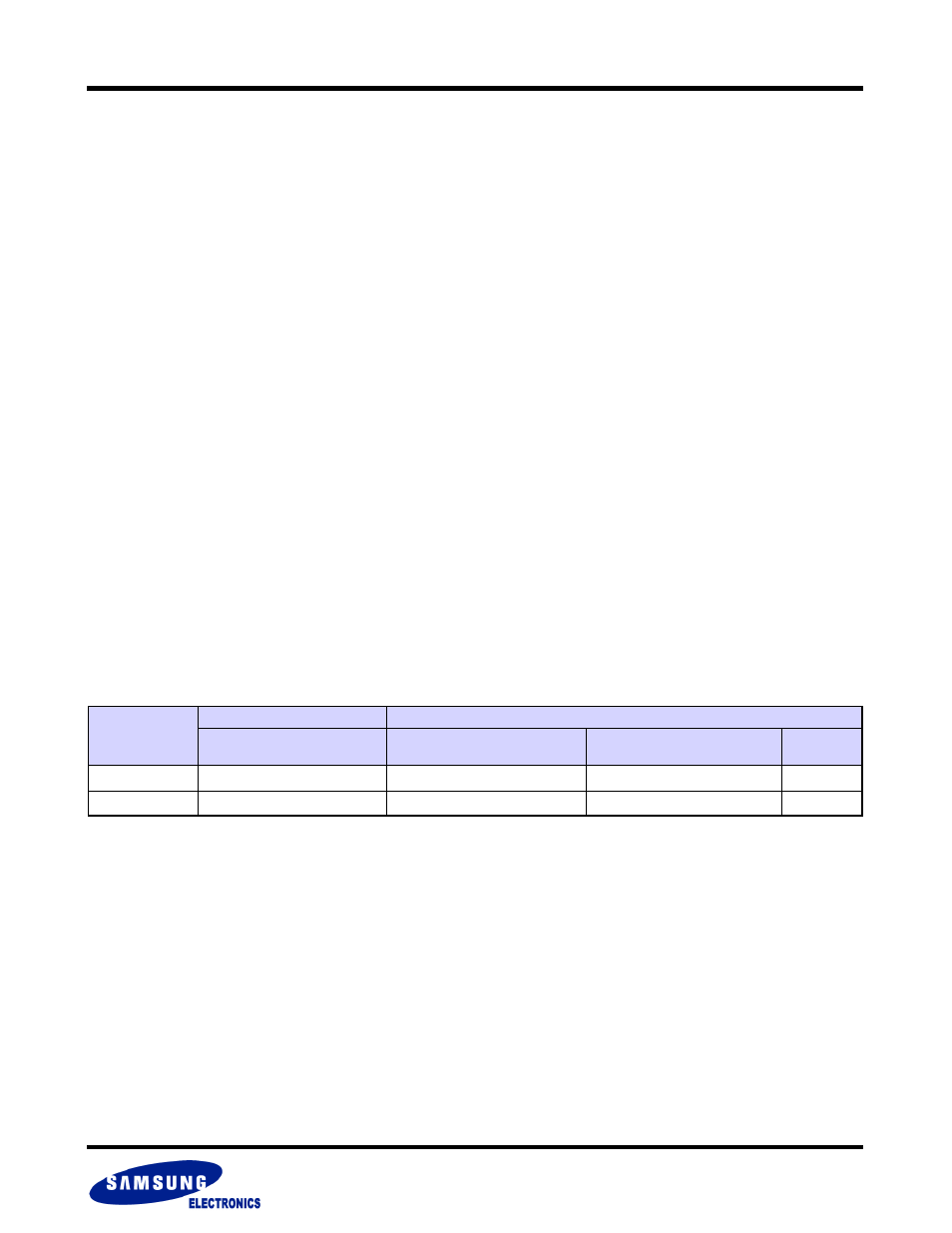

ECC Code and ECC Result by ECC Operation

NOTE :

1) Pre-written ECC code : ECC code which is previously written to NAND Flash Spare Area in program operation.

Operation

Program operation

Load operation

ECC Code Update to NAND

Flash Array Spare Area

ECC Code at BufferRAM Spare

Area

ECC Status & Result Update

to Registers

1bit~4bit

Error

ECC operation

Update

Pre-written ECC code

1)

loaded

Update

Correct

ECC bypass

Not update

Pre-written code

1)

loaded

Invalid

Not correct