5 data protection during power down operation, 6 load operation, Flex-muxonenand4g(kfm4gh6q4m-debx) – Samsung FLEX-MUXONENAND KFN8GH6Q4M User Manual

Page 65

Flex-MuxOneNAND4G(KFM4GH6Q4M-DEBx)

- 65 -

FLASH MEMORY

Flex-MuxOneNAND8G(KFN8GH6Q4M-DEBx)

Flex-MuxOneNAND16G(KFKAGH6Q4M-DEBx)

3.5 Data Protection During Power Down Operation

See Timing Diagrams 6.19

The device is designed to offer protection from any involuntary program/erase during power-transitions.

RP pin which provides hardware protection is recommended to be kept at VIL before Vcc drops to 1.5V.

3.6 Load Operation

See Timing Diagrams 6.9

The Load operation is initiated by setting up the start address from which the data is to be loaded. The Load command is issued in order to ini-

tiate the load.

During a Load operation, the device:

-Transfers the data from NAND Flash array into the BufferRAM

-ECC is checked and any detected and corrected error is reported in the status response as well as

any unrecoverable error.

Once the BufferRAM has been filled, an interrupt is issued to the host so that the contents of the BufferRAM can be read. The read from the

BufferRAM can be an asynchronous read mode or synchronous read mode. The status information related to load operation can be checked

by the host if required.

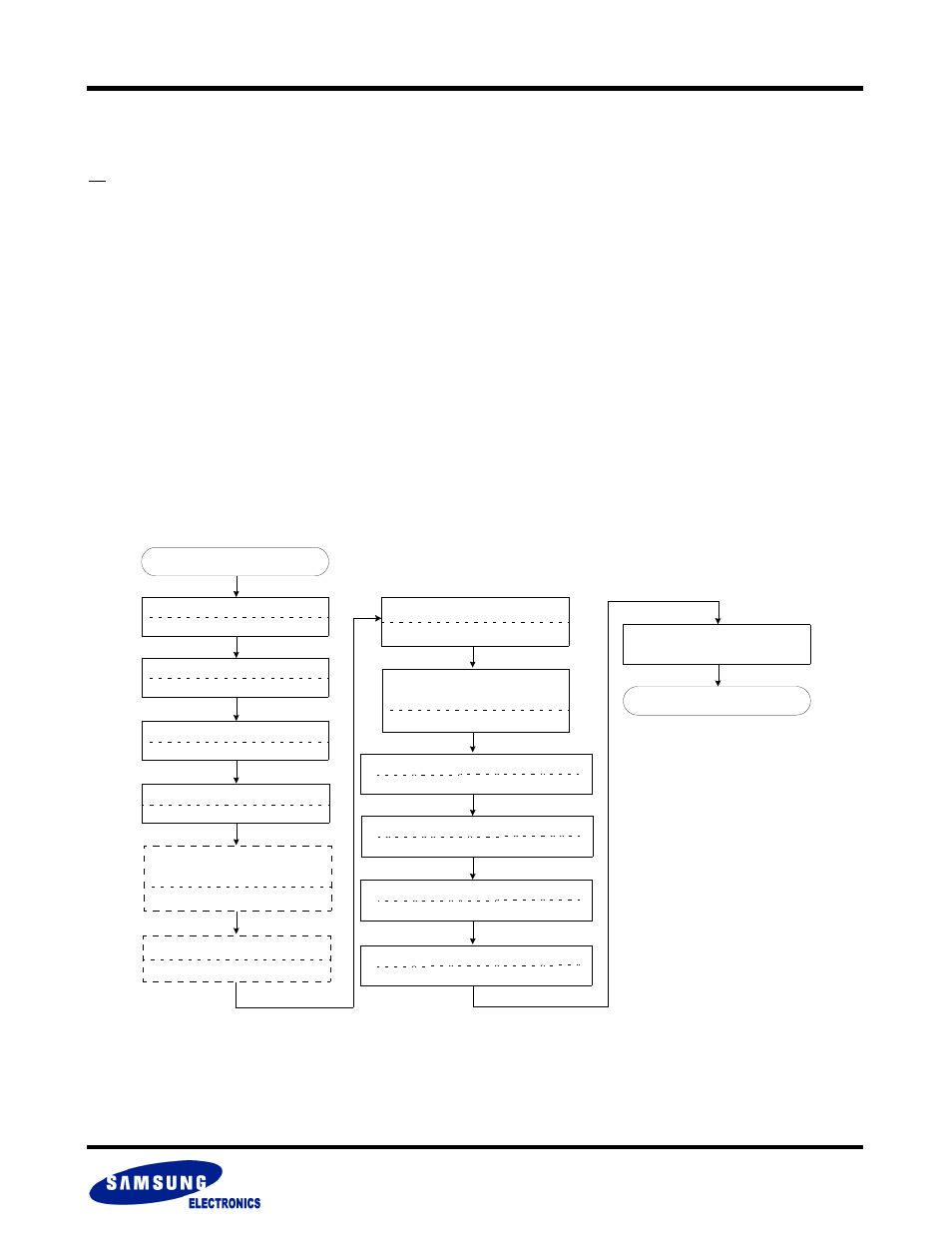

Load Operation Flow Chart Diagram

NOTE :

1) BSA must be 1000.

2) ‘Write 0 to interrupt register’ step may be ignored when using INT auto mode. Refer to chapter 2.8.18.1

Start

Write ‘DFS*, FBA’ of Flash

Add: F100h DQ=DFS, FBA

Write ‘FPA, FSA’ of Flash

Add: F107h DQ=FPA, FSA

Select DataRAM for DDP

Add: F101h DQ=DBS

Wait for INT register

low to high transition

Add: F241h DQ[15]=INT

Write 0 to interrupt register

2)

Add: F241h DQ=0000h

Write ‘BSA

1)

, BSC’ of DataRAM

Add: F200h DQ=0800h

* DBS, DFS is for DDP

Host reads data from

DataRAM

Read completed

Write ‘Load’ Command

Add: F220h DQ=0000h

Write System Configuration

Add: F221h DQ=ECC

Register

Read ECC Status Register1

Add: FF00h DQ=ER1[12:8], ER0[4:0]

Read ECC Status Register2

Add: FF01h DQ=ER3[12:8], ER2[4:0]

Read ECC Status Register3

Add: FF02h DQ=ER5[12:8], ER4[4:0]

Read ECC Status Register4

Add: FF03h DQ=ER7[12:8], ER6[4:0]