7 ac characteristics for asynchronous write, 8 ac characteristics for burst write operation, Flex-muxonenand4g(kfm4gh6q4m-debx) – Samsung FLEX-MUXONENAND KFN8GH6Q4M User Manual

Page 113

Flex-MuxOneNAND4G(KFM4GH6Q4M-DEBx)

- 113 -

FLASH MEMORY

Flex-MuxOneNAND8G(KFN8GH6Q4M-DEBx)

Flex-MuxOneNAND16G(KFKAGH6Q4M-DEBx)

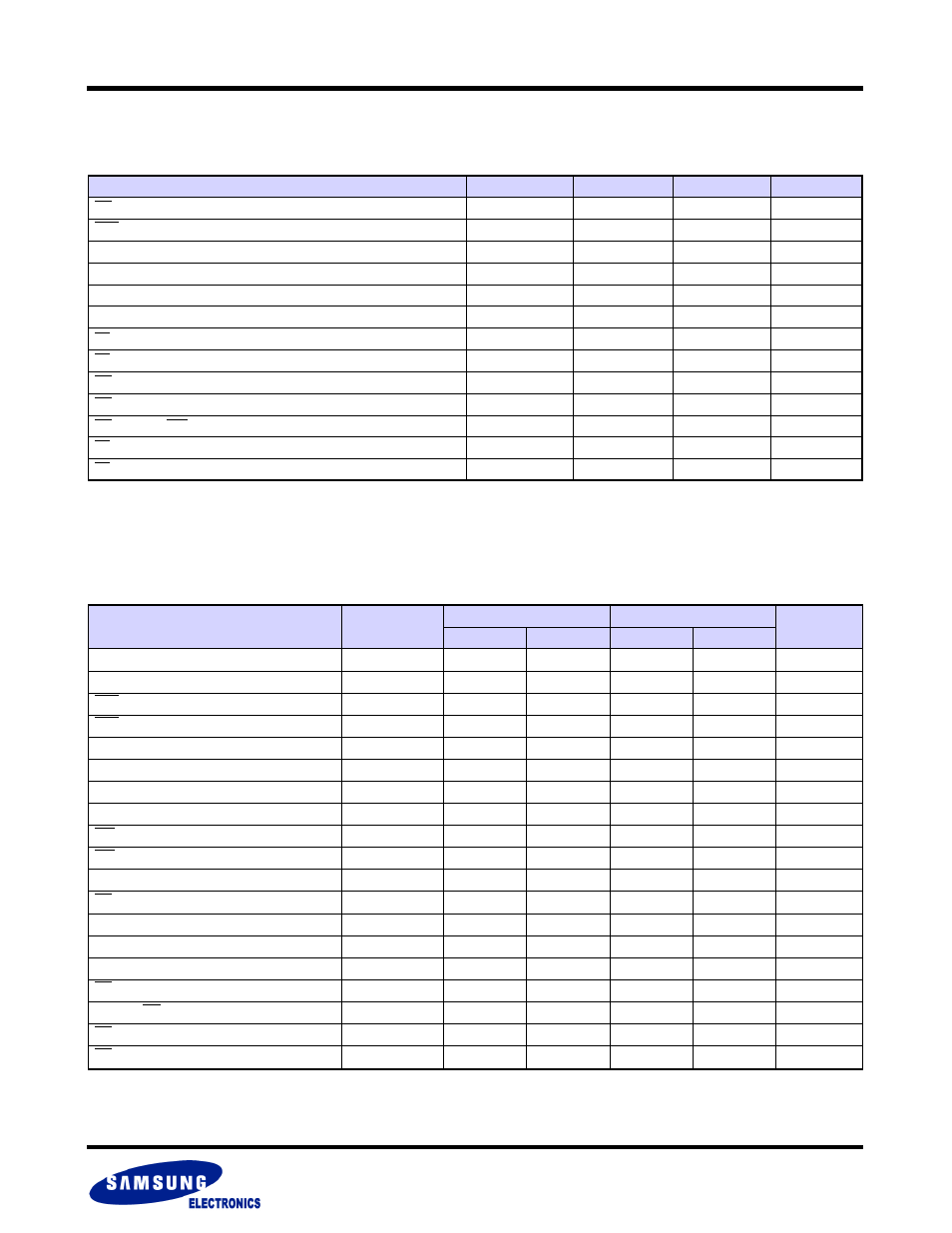

5.7 AC Characteristics for Asynchronous Write

See Timing Diagrams 6.5

5.8 AC Characteristics for Burst Write Operation

See Timing Diagrams 6.6, 6.7 and 6.8.

NOTE :

1)Target Clock frequency is 83Mhz

Parameter

Symbol

Min

Max

Unit

WE Cycle Time

t

WC

70

-

ns

AVD low pulse width

t

AVDP

12

-

ns

Address Setup Time

t

AAVDS

5

-

ns

Address Hold Time

t

AAVDH

6

-

ns

Data Setup Time

t

DS

30

-

ns

Data Hold Time

t

DH

0

-

ns

CE Setup Time

t

CS

0

-

ns

CE Hold Time

t

CH

0

-

ns

WE Pulse Width

t

WPL

40

-

ns

WE Pulse Width High

t

WPH

30

-

ns

WE Disable to AVD Enable

t

WEA

15

-

ns

CE Low to RDY Valid

t

CER

-

15

ns

CE Disable to Output & RDY High Z

t

CEZ

-

20

ns

Parameter

Symbol

66MHz

83MHz

Unit

Min

Max

Min

Max

Clock

CLK

1)

1

66

1

83

MHz

Clock Cycle

t

CLK

15

-

12

-

ns

AVD Setup to CLK

t

AVDS

5

-

4

-

ns

AVD Hold Time from CLK

t

AVDH

2

-

2

-

ns

Address Setup Time to CLK

t

ACS

5

-

4

-

ns

Address Hold Time from CLK

t

ACH

6

-

6

-

ns

Data Setup Time to CLK

t

WDS

5

-

4

-

ns

Data Hold Time from CLK

t

WDH

2

-

2

-

ns

WE Setup Time to CLK

t

WES

5

-

4

-

ns

WE Hold Time from CLK

t

WEH

6

-

6

-

ns

CLK High or Low Time

t

CLKH/L

t

CLK

/3

-

5

-

ns

CE high pulse width

t

CEHP

10

-

10

-

ns

CLK to RDY Valid

t

RDYO

-

11

-

9

ns

CLK to RDY Setup Time

t

RDYA

-

11

-

9

ns

RDY Setup Time to CLK

t

RDYS

4

-

3

-

ns

CE low to RDY valid

t

CER

-

15

-

15

ns

Clock to CE disable

t

CEH

2

t

CLK

-4.5

2

t

CLK

-4.5

ns

CE Setup Time to CLK

t

CES

6

-

4.5

-

ns

CE Disable to Output & RDY High Z

t

CEZ

-

20

-

20

ns