22 interrupt status register f241h (r/w), Flex-muxonenand4g(kfm4gh6q4m-debx) – Samsung FLEX-MUXONENAND KFN8GH6Q4M User Manual

Page 51

Flex-MuxOneNAND4G(KFM4GH6Q4M-DEBx)

- 51 -

FLASH MEMORY

Flex-MuxOneNAND8G(KFN8GH6Q4M-DEBx)

Flex-MuxOneNAND16G(KFKAGH6Q4M-DEBx)

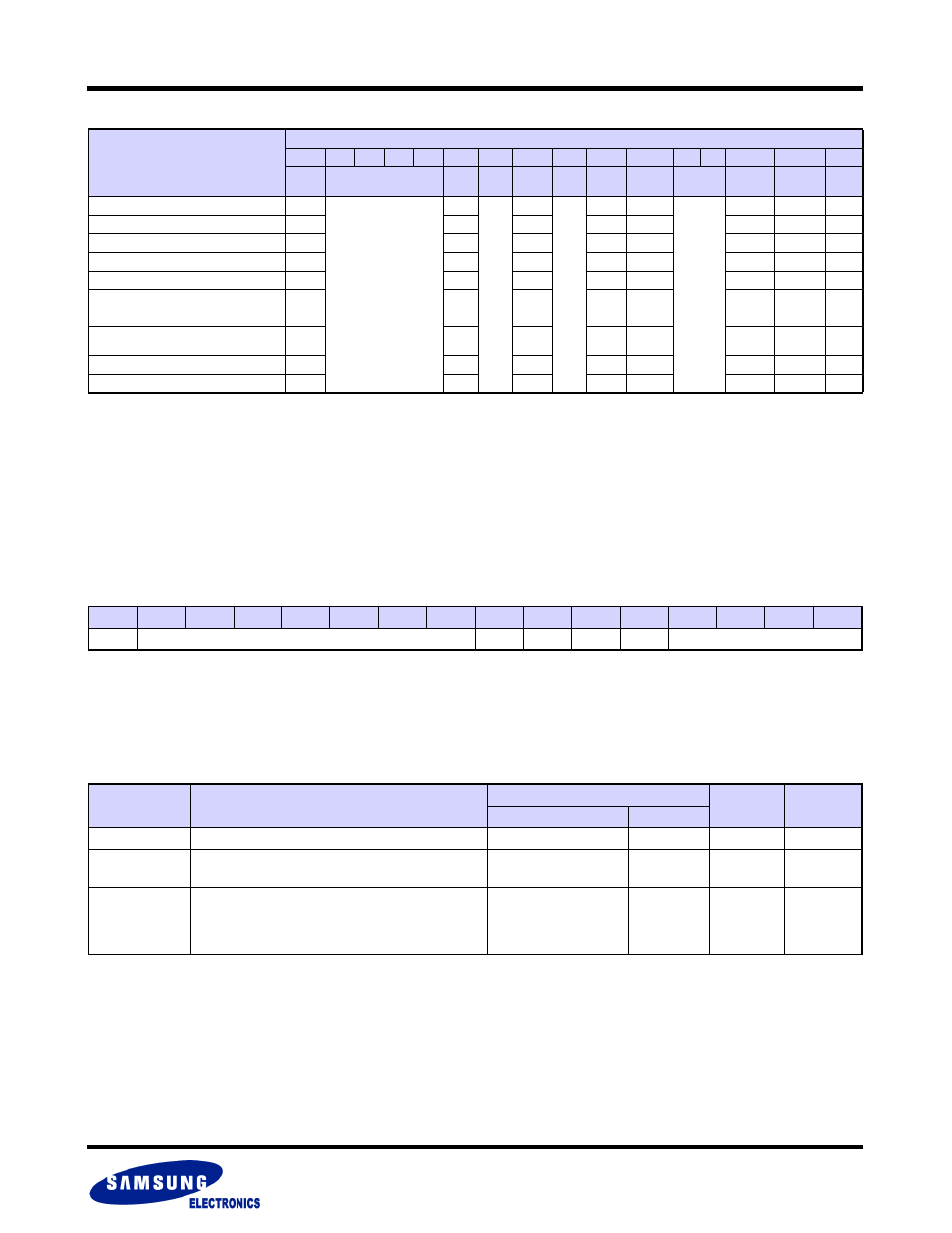

Controller Status Register Output Modes

NOTE :

1) "1" for PI

L

Block Lock, "0" for PI

L

Block Unlock.

2) "1" for 1st Block OTP Lock, "0" for 1st Block OTP Unlock.

3) "1" for OTP Block Lock, "0" for OTP Block Unlock.

4) After Finish Cache Program operation, pass/fail status of Current Cache Program and Previous Cache Program will be updated.

2.8.22 Interrupt Status Register F241h (R/W)

This Read/Write register shows status of the Flex-MuxOneNAND interrupts.

F241h, defaults = 8080h after Cold Reset; 8010h after Warm/Hot Reset

Interrupt (INT)

This is the master interrupt bit. The INT bit is wired directly to the INT pin on the chip. Upon writing '0' to the INT bit, the INT pin goes low if

INTpol is high and goes high if INTpol is low.

INT Interrupt [15]

Mode

Controller Status Register [15:0]

[15]

[14]

[13]

[12]

[11]

[10]

[9]

[8]

[7]

[6]

[5]

[4]

[3]

[2]

[1]

[0]

OnGo

Reserved

Error

Reser

ved

PI

L

1)

Reser

ved

OTP

L

2) OTPB

L

3) Reserved Previous Current

TO

Operation Ongoing

1

0000

0

0

0/1

0

0/1

0/1

00

0

0

0

Operation OK

0

0

0/1

0/1

0/1

0

0

0

Operation Fail

0

1

0/1

0/1

0/1

0

0

0

Program fail on Cache Program

0

1

0/1

0/1

0/1

0

1

0

Previous program fail during Cache Program

0

1

0/1

0/1

0/1

1

0

0

Program fail after Finish Cache Program

0

1

0/1

0/1

0/1

(Note 4)

(Note 4)

0

Reset during Program/Erase/Load

0

0

0/1

0/1

0/1

0

0

0

Program/Erase to the locked block,

Load to the BootRAM

0

1

0/1

0/1

0/1

0

0

0

OTP Program Fail(Lock)

0

1

0/1

1

1

0

0

0

OTP Program Fail

0

1

0/1

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

INT

Reserved(0000000)

RI

WI

EI

RSTI

Reserved(0000)

Status

Conditions

Default State

Valid

State

Interrupt

Function

Cold

Warm/hot

1

1

0

off

sets itself to ‘1’

Commands in the command table in page43 (Refer

to Chapter 2.8.18) are completed.

0

→

1

Pending

clears to ‘0’

‘0’ is written to this bit,

Cold/Warm/Hot reset is being performed, or

command is written to Command Register in INT

auto mode

1

→

0

off