Flex-muxonenand4g(kfm4gh6q4m-debx) – Samsung FLEX-MUXONENAND KFN8GH6Q4M User Manual

Page 52

Flex-MuxOneNAND4G(KFM4GH6Q4M-DEBx)

- 52 -

FLASH MEMORY

Flex-MuxOneNAND8G(KFN8GH6Q4M-DEBx)

Flex-MuxOneNAND16G(KFKAGH6Q4M-DEBx)

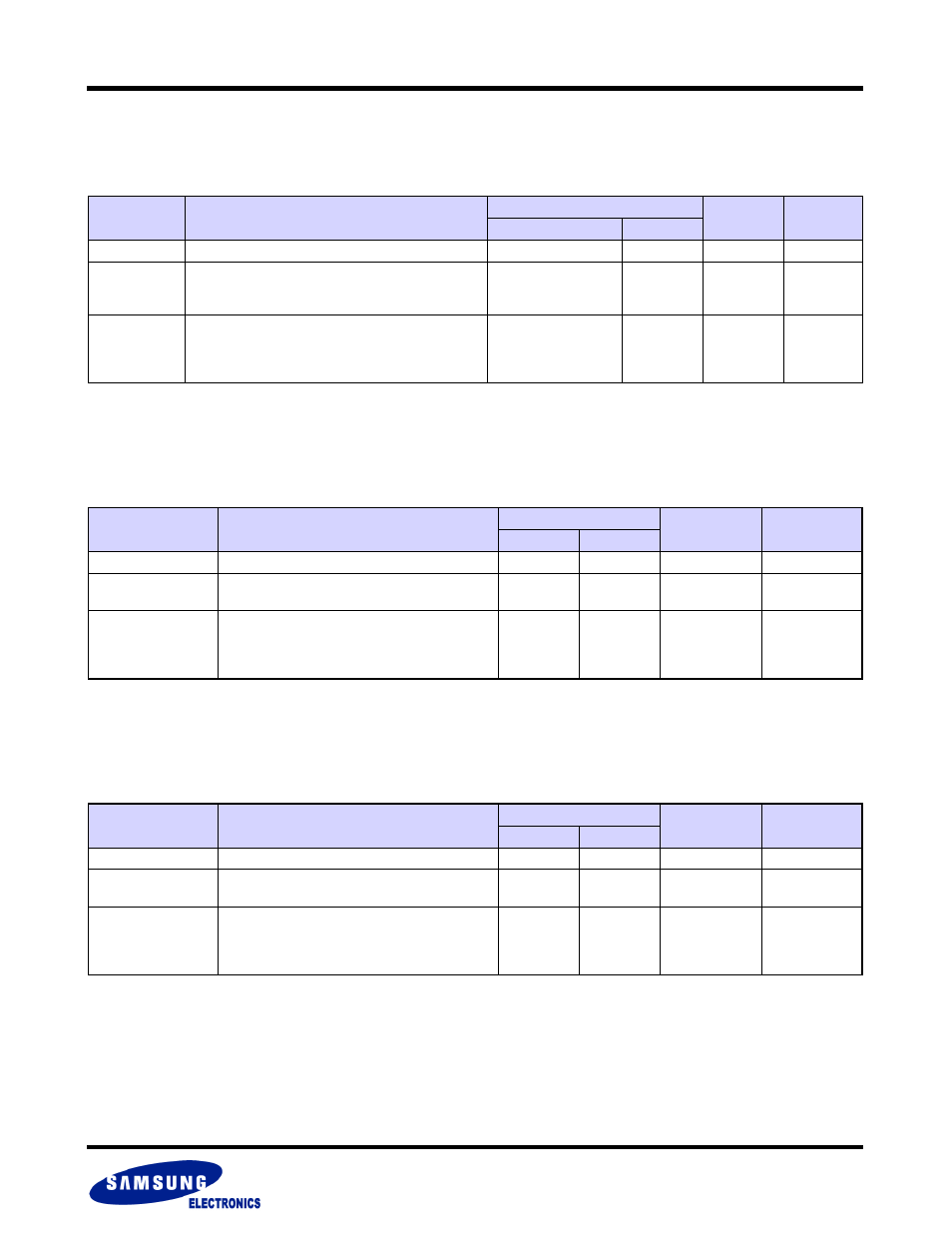

Read Interrupt (RI)

This is the Read interrupt bit.

RI Interrupt [7]

Write Interrupt (WI)

This is the Write interrupt bit.

WI Interrupt [6]

Erase Interrupt (EI)

This is the Erase interrupt bit.

EI Interrupt [5]

Status

Conditions

Default State

Valid

State

Interrupt

Function

Cold

Warm/hot

1

0

0

off

sets itself to ‘1’

At the completion of a Load, Superload or LSB Page

Recovery Read Operation.

(0000h, 0003h or 0005h)

0

→

1

Pending

clears to ‘0’

‘0’ is written to this bit,

Cold/Warm/Hot reset is being performed, or

command is written to Command Register in INT auto

mode

1

→

0

off

Status

Conditions

Default State

Valid

State

Interrupt

Function

Cold

Warm/hot

0

0

0

off

sets itself to ‘1’

At the completion of an Program Operation

(0080h and 007Fh)

0

→

1

Pending

clears to ‘0’

‘0’ is written to this bit,

Cold/Warm/Hot reset is being performed, or com-

mand is written to Command Register in INT auto

mode

1

→

0

off

Status

Conditions

Default State

Valid

State

Interrupt

Function

Cold

Warm/hot

0

0

0

off

sets itself to ‘1’

At the completion of an Erase Operation

(0094h and 0030h)

0

→

1

Pending

clears to ‘0’

‘0’ is written to this bit,

Cold/Warm/Hot reset is being performed, or com-

mand is written to Command Register in INT auto

mode

1

→

0

off