13 interleave cache program operation timing, Flex-muxonenand4g(kfm4gh6q4m-debx) – Samsung FLEX-MUXONENAND KFN8GH6Q4M User Manual

Page 124

Flex-MuxOneNAND4G(KFM4GH6Q4M-DEBx)

- 124 -

FLASH MEMORY

Flex-MuxOneNAND8G(KFN8GH6Q4M-DEBx)

Flex-MuxOneNAND16G(KFKAGH6Q4M-DEBx)

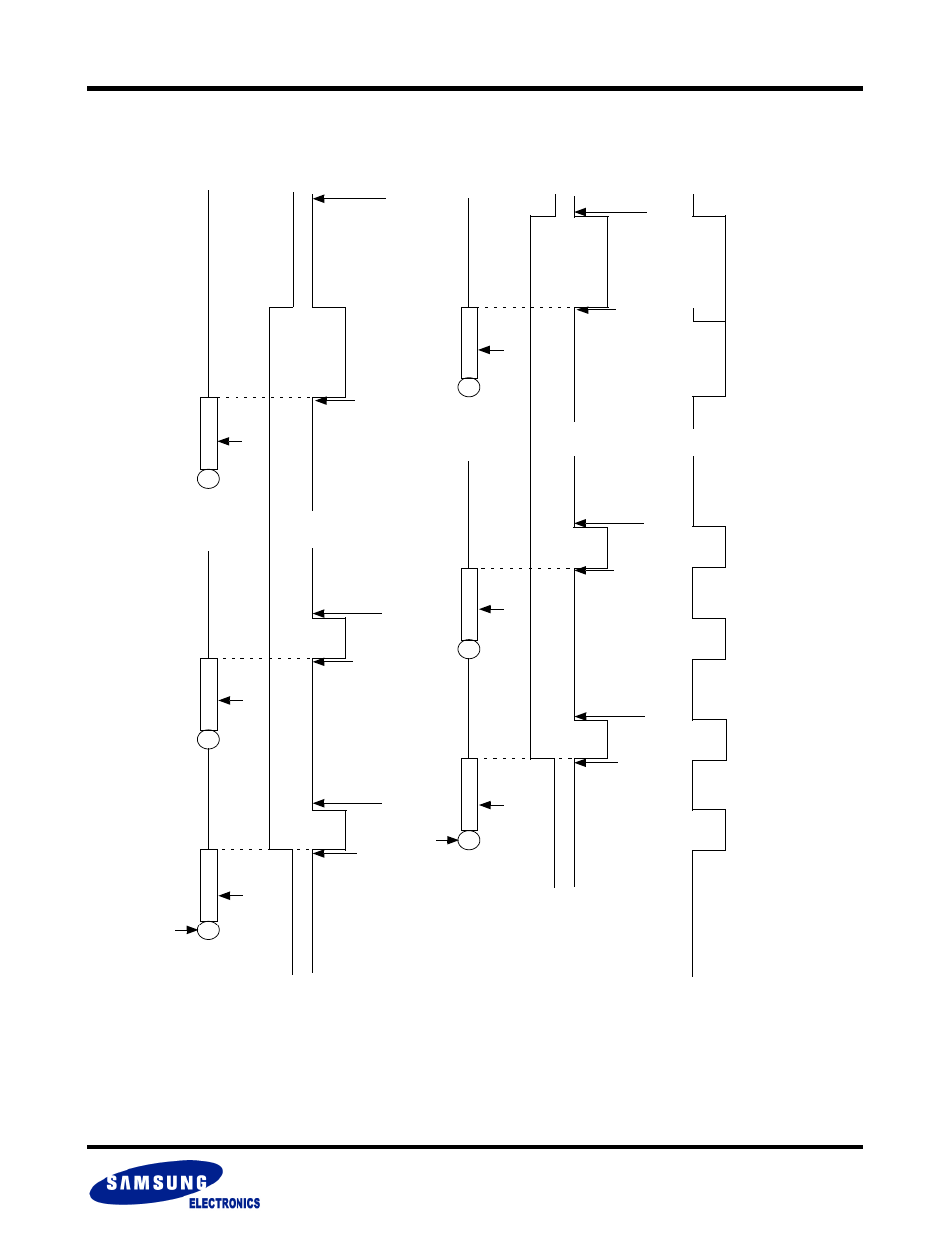

6.13 Interleave Cache Program Operation Timing

See AC Characteristics Table 5.7 and Table 5.9

1s

t dat

a i

n

put

2nd dat

a input

Add

ress Se

tt

in

g

ca

ch

e pro

g

ram

C

o

m

m

an

d

ADQ0~

A1, A2, An : Address of D

at

aRAM to be w

ritten.

INT

: Indica

tor for

Dat

aRAM’

s S

tatus (Rea

dy=High, Busy=Lo

w

)

Ongoing S

ta

tus : In

dicated by OnGo bit in

Con

troller

S

ta

tus R

egister

[15] (F

240h)

4KB dat

a input : Asynch W

rite / Synch

W

rite available.

Command

input

and INT

bit o

r pin behavior

is based on ‘INT

auto mode’.

NO

TE : 1) IN

T pi

n m

ight

to

ggle w

h

en

INT

bit of

ch

ip1 tu

rns

to r

eady before

host i

ssues ‘

p

rogr

am’

comma

nd

on

ch

ip

2.

ADQ15

A1

A2

Hig

h

-Z

IN

T b

it

.

...

.

.

4K

B da

ta

into

2 Da

ta

RAM

s

4KB

da

ta

into

2 Da

taR

A

Ms

Ca

ch

e pro

g

ram

C

o

m

m

an

d

prog

ram

C

o

m

m

an

d

Las

t dat

a i

n

put

An

4K

B da

ta

in

to

2 Da

taR

A

Ms

.

On

goin

g

St

a

tu

s

Co

ntroller S

tatu

s Re

gis

te

r

C

h

e

ck

cu

rrent :

In

va

lid

pre

vio

us

: Pa

ss

=

0

, Fail=

1

Co

ntroller S

tatus

Re

gis

te

r

C

h

e

ck

curren

t

: Pa

ss=0

, F

a

il=1

pre

vio

us

: Pa

ss

=

0

,

F

a

il=

1

.

..

1st

dat

a input

2nd dat

a i

n

put

Ad

dre

ss

S

e

tting

ca

ch

e pr

o

g

ram

C

o

mman

d

AD

Q0~

AD

Q15

A1

A2

.

..

.

.

4

KB d

a

ta

in

to

2 Da

taR

A

Ms

4K

B da

ta

in

to

2 D

a

ta

RA

M

s

Ca

ch

e prog

ram

C

o

m

m

an

d

prog

ra

m

Co

m

m

an

d

Las

t dat

a input

An

4K

B da

ta

in

to

2 Da

ta

RAM

s

.

..

Ongoi

ng

St

a

tu

s

Co

ntroller S

tatus

Re

gis

te

r

C

h

e

ck

cu

rr

e

n

t :

In

va

lid

pre

vio

us

: Pa

ss

=

0

,

F

a

il=

1

Co

nt

ro

ller

S

tat

u

s Re

gi

st

e

r

C

h

e

ck

cu

rr

en

t :

Pa

ss

=0

, F

a

il=1

.

..

.

..

..

.

..

..

.

..

..

Co

ntroller S

tatu

s Re

gis

te

r

C

h

e

ck

cu

rr

e

n

t :

In

va

lid

(

F

ixe

d

to 0)

prev

iou

s: Inv

a

lid (Fix

ed

to

0

)

Co

ntroller S

tatus

Re

giste

r C

h

e

ck

cu

rr

e

n

t :

In

va

lid

(F

ixe

d

to 0)

pre

viou

s: Inv

a

lid (Fix

ed

to

0

)

INT bit

INT Pi

n

.

..

1)

{

{