9 load operation timing, Flex-muxonenand4g(kfm4gh6q4m-debx) – Samsung FLEX-MUXONENAND KFN8GH6Q4M User Manual

Page 120

Flex-MuxOneNAND4G(KFM4GH6Q4M-DEBx)

- 120 -

FLASH MEMORY

Flex-MuxOneNAND8G(KFN8GH6Q4M-DEBx)

Flex-MuxOneNAND16G(KFKAGH6Q4M-DEBx)

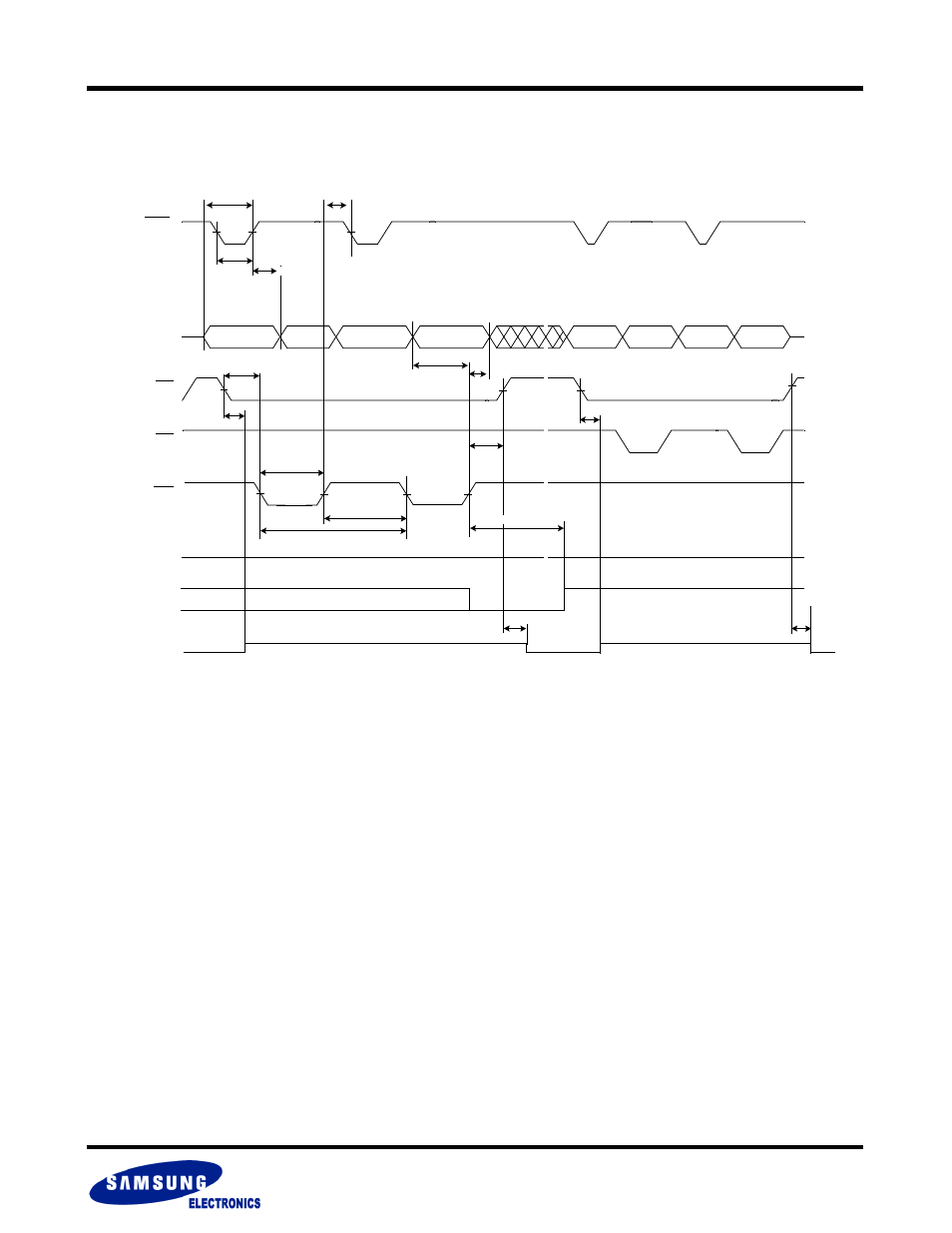

6.9 Load Operation Timing

See AC Characteristics Table 5.7 and Table 5.9

NOTE :

1) AA = Address of address register

CA = Address of command register

LCD = Load Command

LMA = Address of memory to be loaded

BA = Address of BufferRAM to load the data

SA = Address of status register

2) “In progress” and “complete” refer to status register

3) Status reads in this figure is asynchronous read, but status read in synchronous mode is also supported.

t

CER

Load Command Sequence (last two cycles)

WE

CE

CLK

t

AVDP

t

DS

t

DH

t

CH

t

WPL

t

WPH

t

WC

SA

BA

Completed

Da+n

LCD

CA

LMA

AA

ADQ0~15

OE

Read Data

V

IL

≈

≈

≈

≈

≈

≈

t

WEA

t

AAVDS

t

AAVDH

INT

t

CS

AVD

RDY

Hi-Z

t

CER

t

CEZ

bit

t

CEZ

t

RD1 or tRD2