Samsung FLEX-MUXONENAND KFN8GH6Q4M User Manual

Page 83

Flex-MuxOneNAND4G(KFM4GH6Q4M-DEBx)

- 83 -

FLASH MEMORY

Flex-MuxOneNAND8G(KFN8GH6Q4M-DEBx)

Flex-MuxOneNAND16G(KFKAGH6Q4M-DEBx)

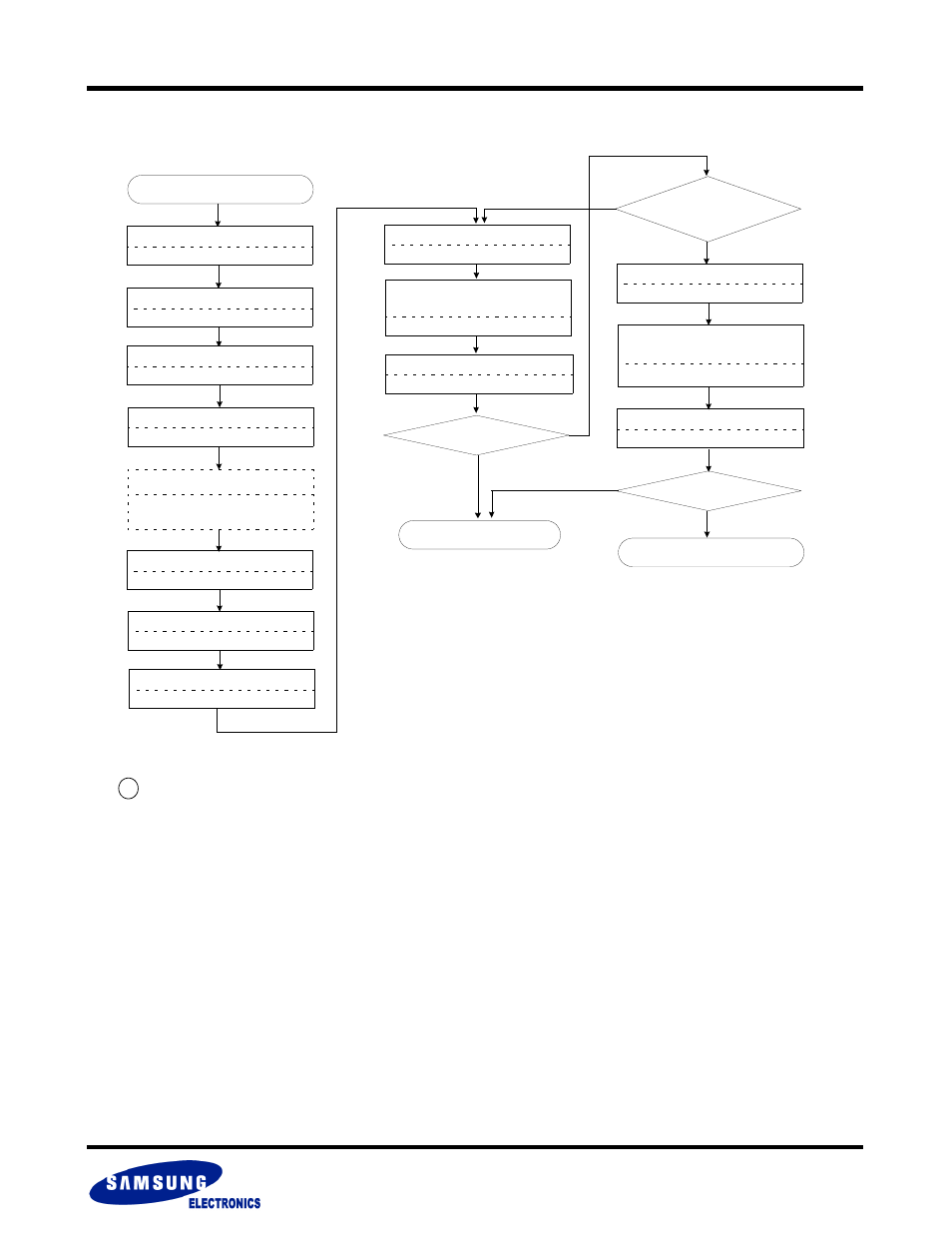

Erase Interleave

1)

(@DDP) Flow Chart

NOTE :

1) Erase Suspend and Erase Resume Operations are not supported in Erase Interleave(@DDP).

Start

Write ‘DFS*, FBA’ of Flash

Add: F100h DQ=DFS*, FBA

Select DataRAM for DDP

Add: F101h DQ=DBS*

Write ‘Erase’ Command

Add: F220h DQ=0094h

Check for INT register high

Add: F241h DQ[15]=INT

Select DataRAM for DDP

Add: F101h DQ=DBS*

INT=1(Ready)

{

1

*

Select DataRAM for DDP

Add: F101h DQ=DBS*

Write ‘DFS*, FBA’ of Flash

Add: F100h DQ=DFS*, FBA

Write ‘Erase’ Command

Add: F220h DQ=0094h

Wait for INT register

Add: F241h DQ=[5]=EI

low to high transition

Select DataRAM for DDP

Add: F101h DQ=DBS*

Read Controller status register

Add: F240 DQ[10]=Error

{

2

*

DQ[10]=0?

NO(Erase Fail)

Erase Error

Has Final Erase

command been issued?

Select DataRAM for DDP

Add: F101h DQ=DBS*

Wait for INT register

low to high transition

Add: F241h DQ[5]=EI

Read Controller status register

Add: F240h DQ[10]=Error

YES(Erase Pass)

DQ[10]=0?

Erase completed

NO

YES

(Final Erase status check)

NO(Erase Fail)

}

3

*

YES(Erase Pass)

Previous Erase Status Check

DBS must be changed to indicate chip. Erase has been issued prior to current erase ongoing

2

*

1

*

Check the chip status before command issues.

Final Erase Status Check

3

*

*

Erase Interleave can work in Auto INT Mode.

Interrupt register must not be written.