4 gpiob1 (b1)—bit 5, 5 gpiob0 (b0)—bit 4, 6 gpioa5 (a5)—bit 3 – Freescale Semiconductor 56F8122 User Manual

Page 87: 7 gpioa4 (a4)—bit 2, 8 gpioa3 (a3)—bit 1, 9 gpioa2 (a2)—bit 0, 9 peripheral clock enable register (sim_pce), This bit selects the alternate function for gpiob1, This bit selects the alternate function for gpiob0, This bit selects the alternate function for gpioa5

Register Descriptions

56F8322 Technical Data, Rev. 10.0

Freescale Semiconductor

87

Preliminary

6.5.8.4

GPIOB1 (B1)—Bit 5

This bit selects the alternate function for GPIOB1.

•

0 = MISO0 (default)

•

1 = RXD1

6.5.8.5

GPIOB0 (B0)—Bit 4

This bit selects the alternate function for GPIOB0.

•

0 = SS0 (default)

•

1 = TXD1

6.5.8.6

GPIOA5 (A5)—Bit 3

This bit selects the alternate function for GPIOA5.

•

0 = PWMA5

•

1 = SCLK1

6.5.8.7

GPIOA4 (A4)—Bit 2

This bit selects the alternate function for GPIOA4.

•

0 = PWMA4

•

1 = MOS1

6.5.8.8

GPIOA3 (A3)—Bit 1

This bit selects the alternate function for GPIOA3.

•

0 = PWMA3

•

1 = MISO1

6.5.8.9

GPIOA2 (A2)—Bit 0

This bit selects the alternate function for GPIOA2.

•

0 = PWMA2

•

1 = SS1

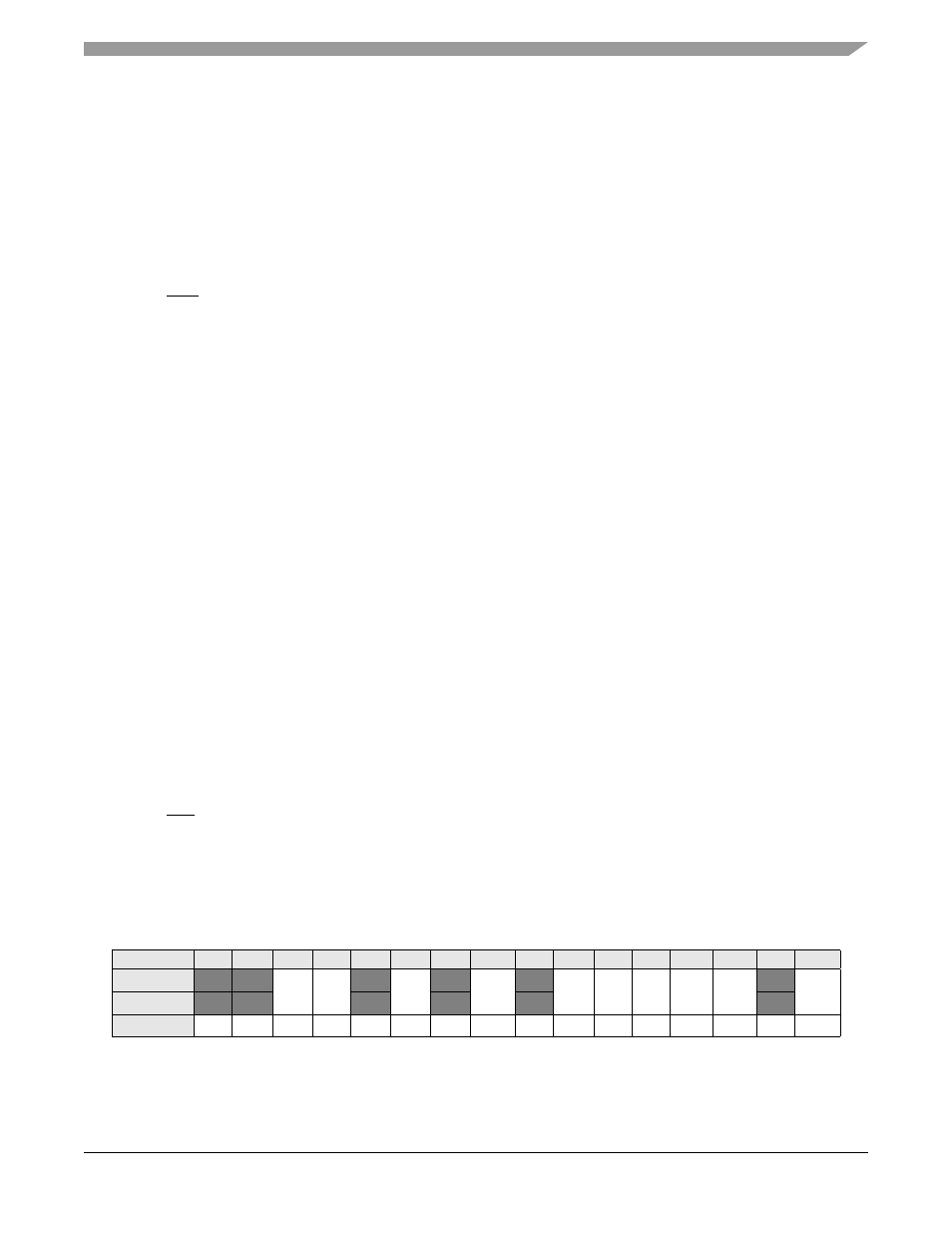

6.5.9

Peripheral Clock Enable Register (SIM_PCE)

The Peripheral Clock Enable register is used to enable or disable clocks to the peripherals as a power

savings feature. The clocks can be individually controlled for each peripheral on the chip.

Figure 6-12 Peripheral Clock Enable Register (SIM_PCE)

Base + $C

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Read

1

1

ADCA

CAN

1

DEC0

1

TMRC

1

TMRA

SCI 1

SCI 0

SPI1

SPI0

1

PWMA

Write

RESET

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1