2 once enable (once ebl)—bit 5, 3 software reset (sw rst)—bit 4, 4 stop disable (stop_disable)—bits 3–2 – Freescale Semiconductor 56F8122 User Manual

Page 81: 5 wait disable (wait_disable)—bits 1–0, 2 sim reset status register (sim_rststs), 1 reserved—bits 15–6, 2 software reset (swr)—bit 5

Register Descriptions

56F8322 Technical Data, Rev. 10.0

Freescale Semiconductor

81

Preliminary

6.5.1.2

OnCE Enable (ONCE EBL)—Bit 5

•

0 = OnCE clock to 56800E core enabled when core TAP is enabled

•

1 = OnCE clock to 56800E core is always enabled

6.5.1.3

Software Reset (SW RST)—Bit 4

Writing 1 to this field will cause the part to reset.

6.5.1.4

Stop Disable (STOP_DISABLE)—Bits 3–2

•

00 = Stop mode will be entered when the 56800E core executes a STOP instruction

•

01 = The 56800E STOP instruction will not cause entry into Stop mode; STOP_DISABLE can be

reprogrammed in the future

•

10 = The 56800E STOP instruction will not cause entry into Stop mode; STOP_DISABLE can then only be

changed by resetting the device

•

11 = Same operation as 10

6.5.1.5

Wait Disable (WAIT_DISABLE)—Bits 1–0

•

00 = Wait mode will be entered when the 56800E core executes a WAIT instruction

•

01 = The 56800E WAIT instruction will not cause entry into Wait mode; WAIT_DISABLE can be

reprogrammed in the future

•

10 = The 56800E WAIT instruction will not cause entry into Wait mode; WAIT_DISABLE can then only

be changed by resetting the device

•

11 = Same operation as 10

6.5.2

SIM Reset Status Register (SIM_RSTSTS)

Bits in this register are set upon any system reset and are initialized only by a Power-On Reset (POR). A

reset (other than POR) will only set bits in the register; bits are not cleared. Only software should clear this

register.

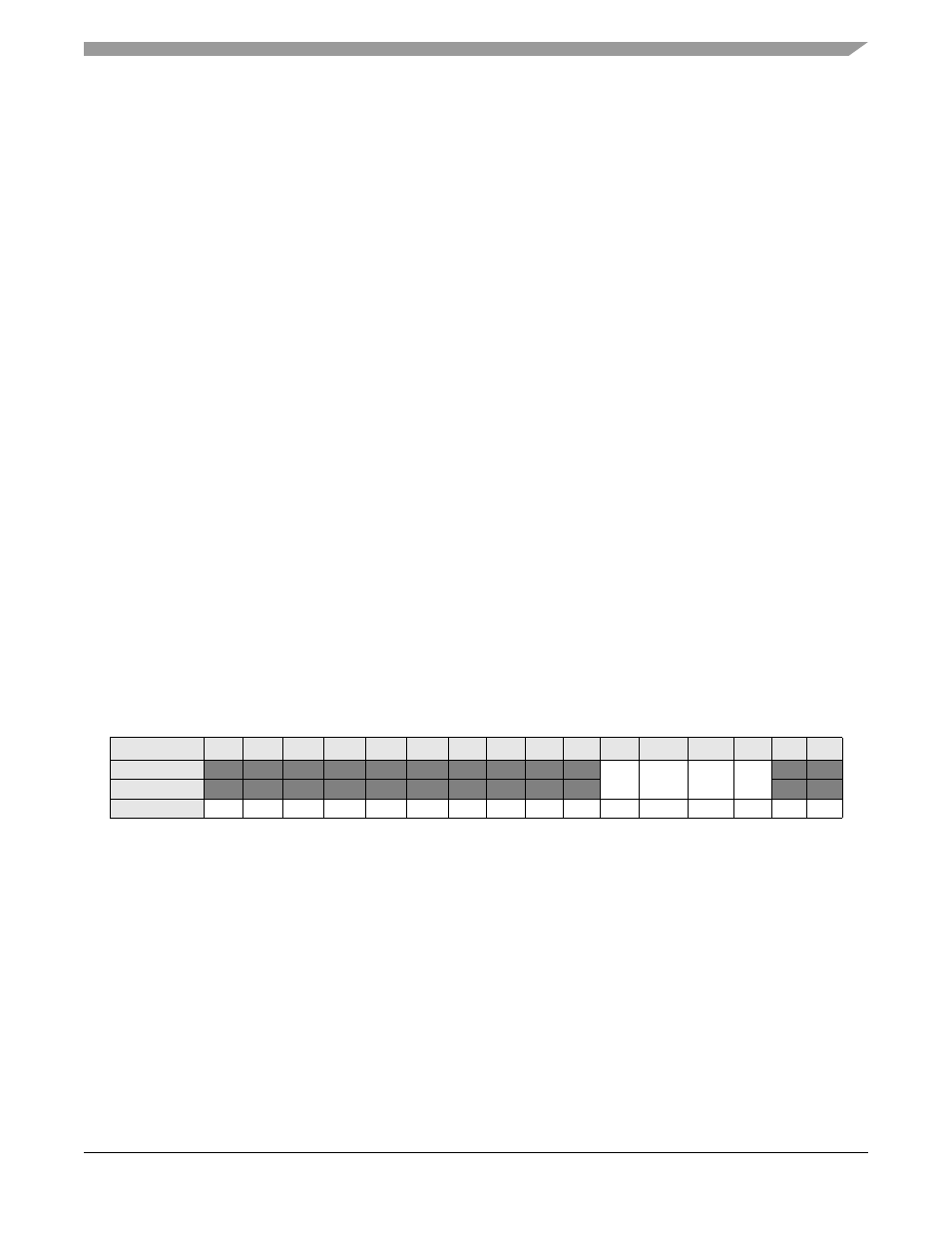

Figure 6-4 SIM Reset Status Register (SIM_RSTSTS)

6.5.2.1

Reserved—Bits 15–6

This bit field is reserved or not implemented. It is read as zero and cannot be modified by writing.

6.5.2.2

Software Reset (SWR)—Bit 5

When 1, this bit indicates that the previous reset occurred as a result of a software reset (write to SW RST

bit in the SIM_CONTROL register). This bit will be cleared by any hardware reset or by software. Writing

a 0 to this bit position will set the bit, while writing a 1 to the bit will clear it.

Base + $1

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Read

0

0

0

0

0

0

0

0

0

0

SWR

COPR

EXTR

POR

0

0

Write

RESET

0

0

0

0

0

0

0

0

0

0

0

0