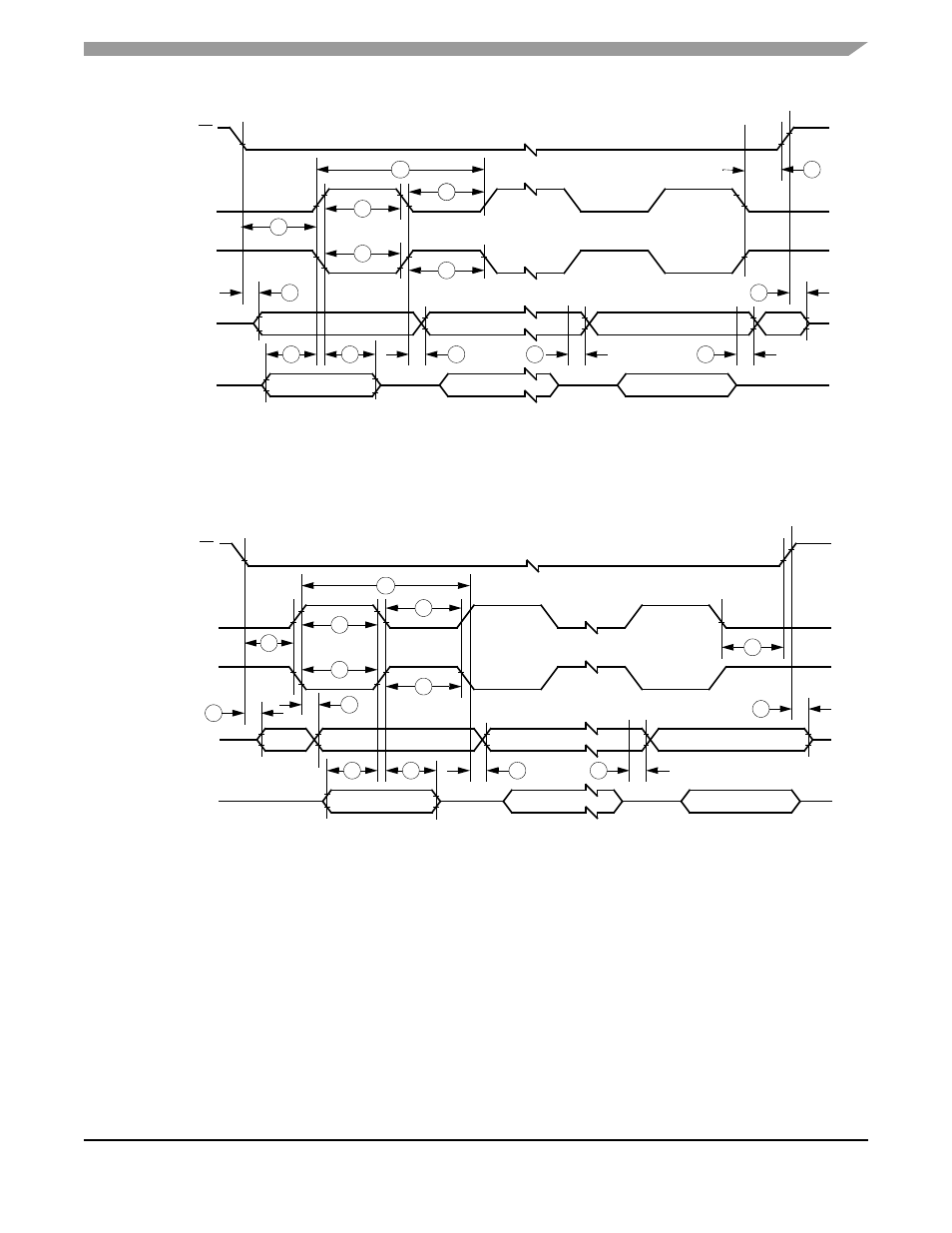

Figure 19-2, Figure 19-2. spi slave timing – Freescale Semiconductor MC68HC908MR32 User Manual

Page 271

Serial Peripheral Interface Characteristics

MC68HC908MR32 • MC68HC908MR16 Data Sheet, Rev. 6.1

Freescale Semiconductor

271

Figure 19-2. SPI Slave Timing

Note: Not defined, but normally MSB of character just received

SLAVE

SS

INPUT

SPCK, CPOL = 0

INPUT

SPCK, CPOL = 1

INPUT

MISO

INPUT

MOSI

OUTPUT

4

5

5

1

4

MSB IN

BITS 6–1

8

6

10

11

11

NOTE

SLAVE LSB OUT

9

3

LSB IN

2

7

BITS 6–1

MSB OUT

Note: Not defined, but normally LSB of character previously transmitted

SLAVE

SS

INPUT

SPCK, CPOL = 0

INPUT

SPCK, CPOL = 1

INPUT

MISO

INPUT

MOSI

OUTPUT

4

5

5

1

4

MSB IN

BITS 6–1

8

6

10

NOTE

SLAVE LSB OUT

9

3

LSB IN

2

7

BITS 6–1

MSB OUT

10

a) SPI Slave Timing (CPHA = 0)

b) SPI Slave Timing (CPHA = 1)

11

11

This manual is related to the following products: