3 break status register, 4 tbreak flag control register, 3 monitor rom (mon) – Freescale Semiconductor MC68HC908MR32 User Manual

Page 255: Break status register, Break flag control register, Monitor rom (mon)

Monitor ROM (MON)

MC68HC908MR32 • MC68HC908MR16 Data Sheet, Rev. 6.1

Freescale Semiconductor

255

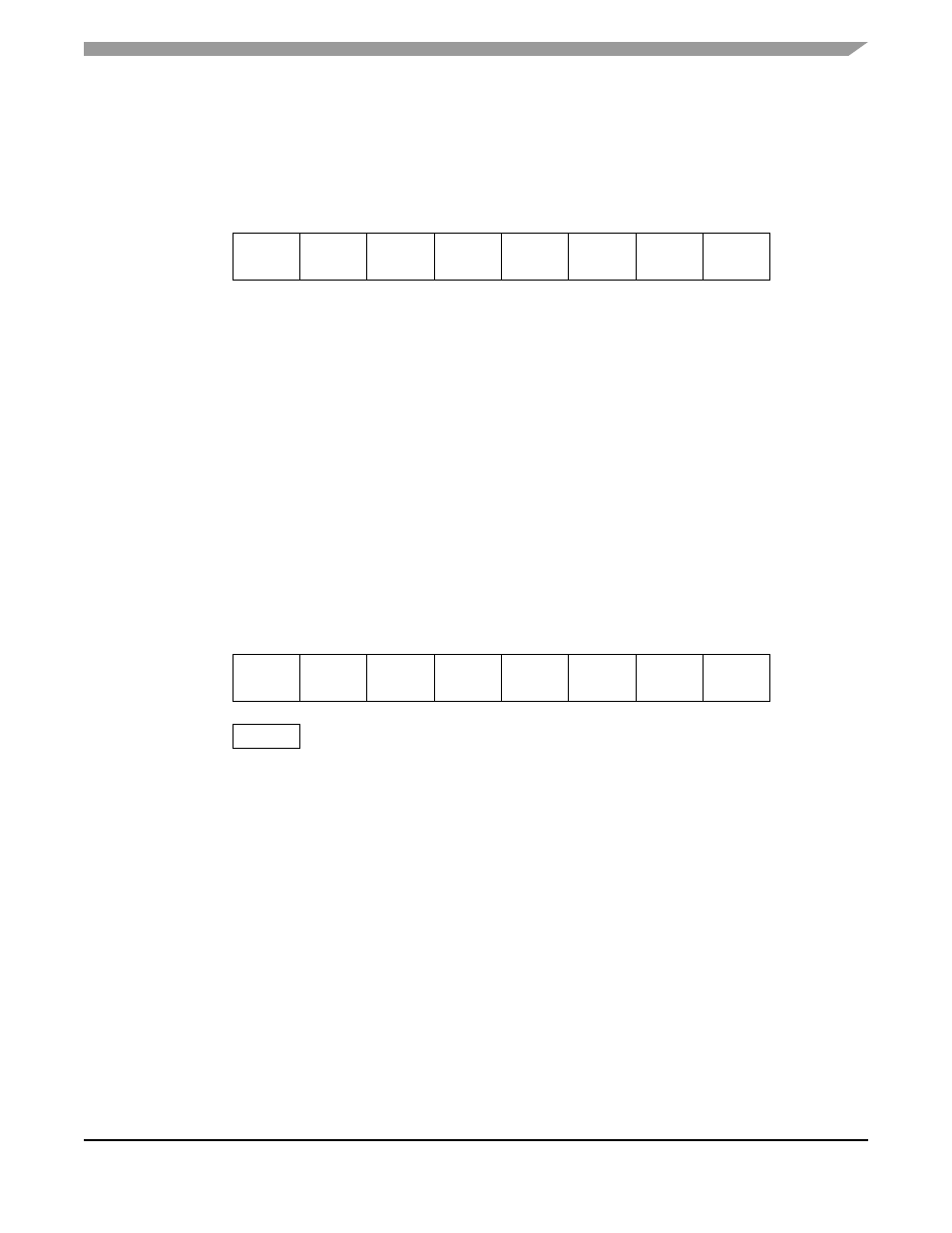

18.2.3.3 Break Status Register

The break status register (SBSR) contains a flag to indicate that a break caused an exit from wait mode.

The flag is useful in applications requiring a return to wait mode after exiting from a break interrupt.

BW — Break Wait Bit

This read/write bit is set when a break interrupt causes an exit from wait mode. Clear BW by writing a

logic 0 to it. Reset clears BW.

1 = Break interrupt during wait mode

0 = No break interrupt during wait mode

BW can be read within the break interrupt routine. The user can modify the return address on the stack

by subtracting 1 from it.

18.2.3.4 Break Flag Control Register

The break flag control register (SBFCR) contains a bit that enables software to clear status bits while the

MCU is in a break state.

BCFE — Break Clear Flag Enable Bit

This read/write bit enables software to clear status bits by accessing status registers while the MCU is

in a break state. To clear status bits during the break state, the BCFE bit must be set.

1 = Status bits clearable during break

0 = Status bits not clearable during break

18.3 Monitor ROM (MON)

The monitor ROM (MON) allows complete testing of the microcontroller unit (MCU) through a single-wire

interface with a host computer. Monitor mode entry can be achieved without the use of V

TST

as long as

vector addresses $FFFE and $FFFF are blank, thus reducing the hardware requirements for in-circuit

programming.

Address:

$FE00

Bit 7

6

5

4

3

2

1

Bit 0

Read:

R

R

R

R

R

R

BW

R

Write:

Reset:

0

Figure 18-6. SIM Break Status Register (SBSR)

Address:

$FE03

Bit 7

6

5

4

3

2

1

Bit 0

Read:

BCFE

R

R

R

R

R

R

R

Write:

Reset:

0

R

= Reserved

Figure 18-7. SIM Break Flag Control Register (SBFCR)