1 master mode, Master mode, Figure 15-3 – Freescale Semiconductor MC68HC908MR32 User Manual

Page 198

Serial Peripheral Interface Module (SPI)

MC68HC908MR32 • MC68HC908MR16 Data Sheet, Rev. 6.1

198

Freescale Semiconductor

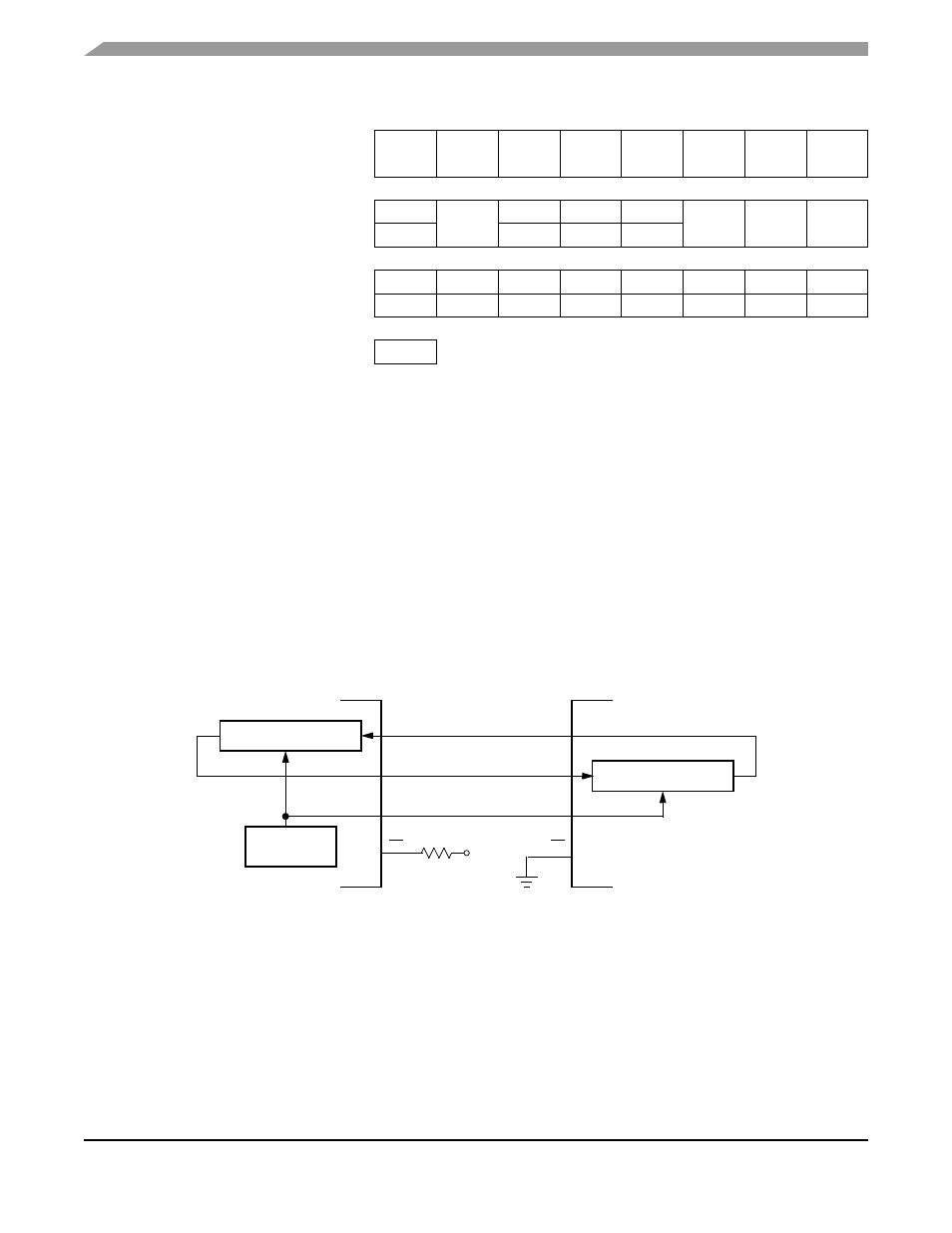

15.4.1 Master Mode

The SPI operates in master mode when the SPI master bit, SPMSTR, is set.

NOTE

Configure the SPI modules as master or slave before enabling them.

Enable the master SPI before enabling the slave SPI. Disable the slave SPI

before disabling the master SPI. See

Only a master SPI module can initiate transmissions. Software begins the transmission from a master SPI

module by writing to the SPI data register. If the shift register is empty, the byte immediately transfers to

the shift register, setting the SPI transmitter empty bit, SPTE. The byte begins shifting out on the MOSI

pin under the control of the serial clock. See

Figure 15-4. Full-Duplex Master-Slave Connections

The SPR1 and SPR0 bits control the baud rate generator and determine the speed of the shift register.

See

15.12.2 SPI Status and Control Register

. Through the SPSCK pin, the baud-rate generator of the

master also controls the shift register of the slave peripheral.

As the byte shifts out on the MOSI pin of the master, another byte shifts in from the slave on the master’s

MISO pin. The transmission ends when the receiver full bit, SPRF, becomes set. At the same time that

SPRF becomes set, the byte from the slave transfers to the receive data register. In normal operation,

Addr.

Register Name

Bit 7

6

5

4

3

2

1

Bit 0

$0044

SPI Control Register

(SPCR)

Read:

SPRIE

R

SPMSTR

CPOL

CPHA

SPWOM

SPE

SPTIE

Write:

Reset:

0

0

1

0

1

0

0

0

$0045

SPI Status and Control

Register (SPSCR)

Read:

SPRF

ERRIE

OVRF

MODF

SPTE

MODFEN

SPR1

SPR0

Write:

R

R

R

R

Reset:

0

0

0

0

1

0

0

0

$0046

SPI Data Register

(SPDR)

Read:

R7

R6

R5

R4

R3

R2

R1

R0

Write:

T7

T6

T5

T4

T3

T2

T1

T0

Reset:

Unaffected by reset

R

= Reserved

Figure 15-3. SPI I/O Register Summary

SHIFT REGISTER

SHIFT REGISTER

BAUD RATE

GENERATOR

MASTER MCU

SLAVE MCU

V

DD

MOSI

MOSI

MISO

MISO

SPSCK

SPSCK

SS

SS