4 altera cyclone iv de2-115 with nios and rgmii, 1 configuration and resource consumption, 2 functionality – BECKHOFF EtherCAT IP Core for Altera FPGAs v3.0.10 User Manual

Page 68: 3 downloadable configuration file, Altera cyclone iv de2-115 with nios and rgmii, Configuration and resource consumption, Functionality, Downloadable configuration file

Example Designs

III-56

Slave Controller

– IP Core for Altera FPGAs

6.4

Altera Cyclone IV DE2-115 with NIOS and RGMII

6.4.1

Configuration and resource consumption

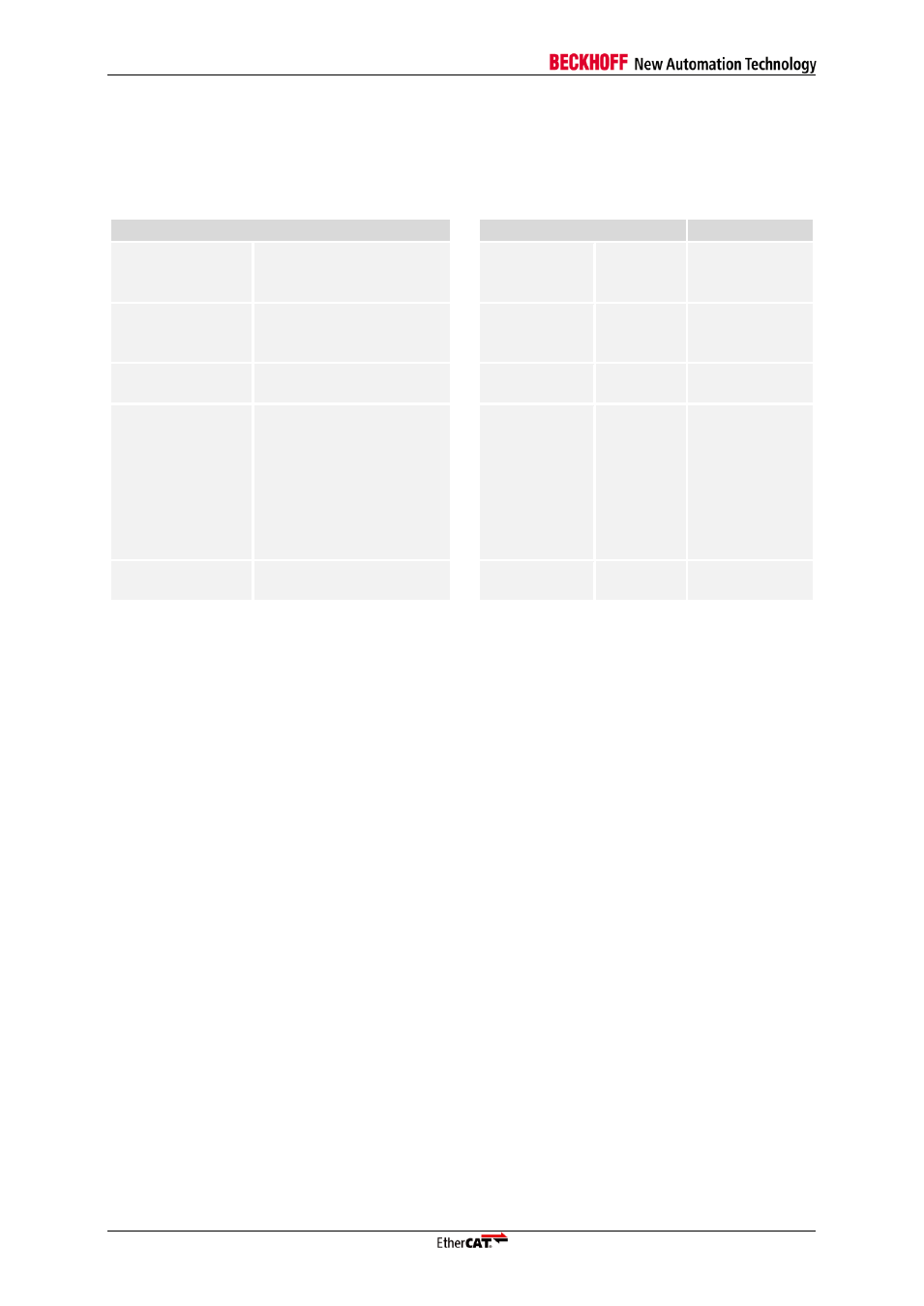

Table 16: Resource consumption NIOS example design DE2-115 RGMII

Configuration

Resources

EP4CE115

Physical layer

2x RGMII,

MIIM, Link state and PHY

configuration through MI

Les

19,182

17 %

Internal Function

3x FMMU

4x SyncManager

1 KB RAM

Registers

9,106

8 %

Distributed clocks

32 bit,

2x Sync, 2x Latch

M9K

264

61 %

Feature details

AL Status Code register,

Extended Watchdog,

AL Event Mask register,

Watchdog counter, EPU

and PDI Error counter,

Lost Link Counter,

RUN_LED,

LED Test

PLLs

1

25 %

PDI

Avalon

32 bit

Multiplier

elements

0

0 %

6.4.2

Functionality

Configure ETHERNET0 and ETHERNET1 for RGMII mode by setting jumpers JP1 and JP2 to 1-2.

The DE2-115 example design with RGMII ports is equal to the DE2-115 example design with MII,

except for the PHY connection. Refer to DE2-115 example design with MII for more details.

6.4.3

Downloadable configuration file

An already synthesized time limited OpenCore Plus configuration file

DE2_115_EtherCAT_NIOS_RGMII_time_limited.sof

based on this digital I/O example design can be found in the

folder. After expiration of about 1 hour the design quits its operation unless the JTAG connection to

Quartus remains active. This file must only be used for evaluation purposes, any distribution is not

allowed.