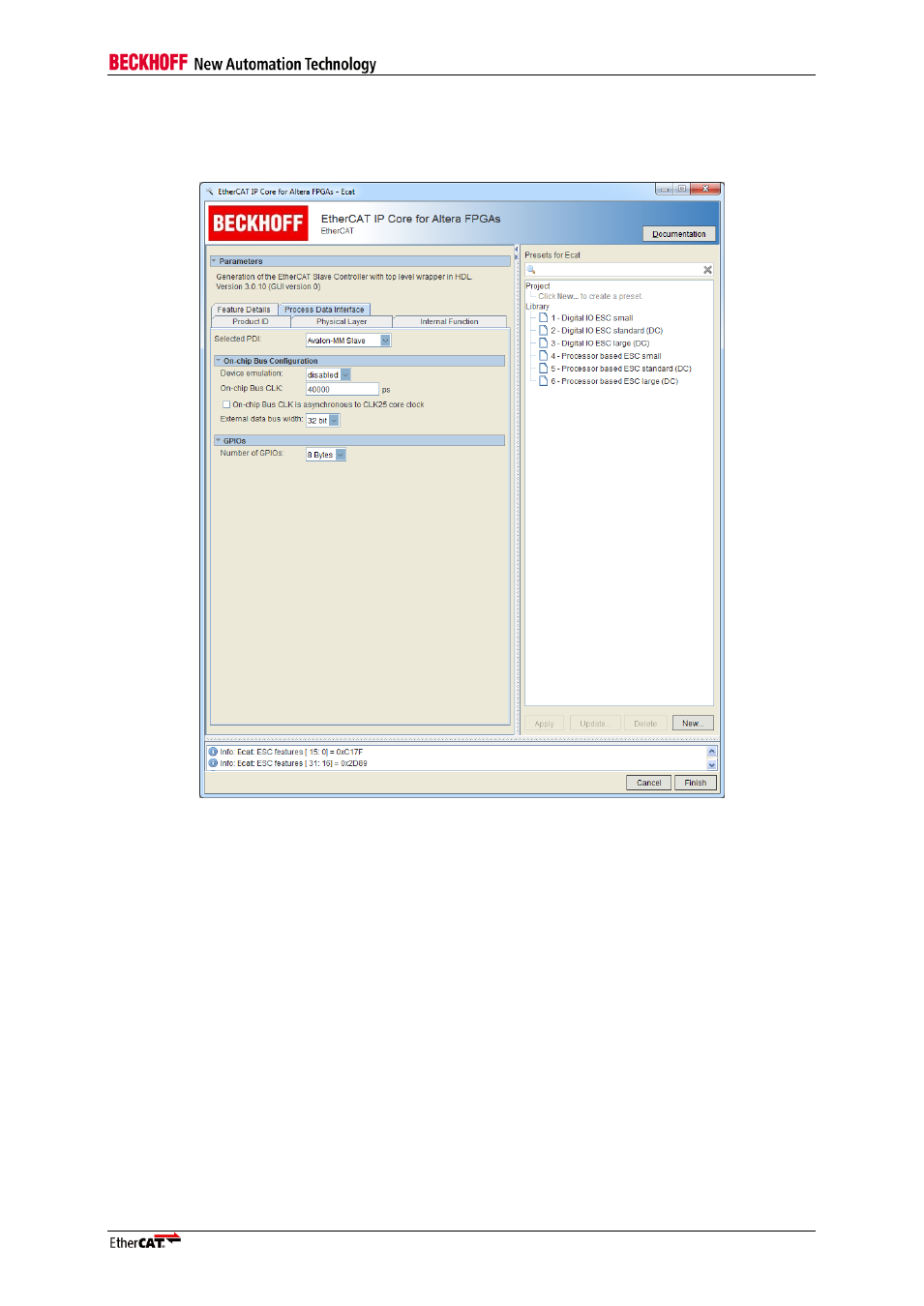

5 avalon configuration, Figure 18: register pdi, Avalon interface configuration – BECKHOFF EtherCAT IP Core for Altera FPGAs v3.0.10 User Manual

Page 59

IP Core Configuration

Slave Controller

– IP Core for Altera FPGAs

III-47

5.2.5.5

Avalon Configuration

The Avalon PDI connects the IP Core with an Avalon Master (e.g., Altera NIOS). The Avalon PDI uses

memory addressing/dynamic bus sizing.

Figure 18: Register PDI

– Avalon Interface Configuration

Device emulation

Enable Device emulation (0x0141[0]=1). This feature should be disabled in most use cases.

On-chip Bus CLK

This is the clock period of the Avalon bus clock for communication between ESC and the Avalon

master. This configuration option is not available if the clock period can be derived from the Qsys

clock connections.

On-Chip Bus CLK is asynchronous to CLK25 core clock

Enable if the On-chip BUS CLK is asynchronous to CLK25. Additional synchronization stages are

added in this case.

External data bus width

Select the Avalon data bus width (8/16/32/64 bit) of the Avalon slave interface.