2 ebv cyclone iv dbc4ce55 with nios, 1 configuration and resource consumption, 2 functionality – BECKHOFF EtherCAT IP Core for Altera FPGAs v3.0.10 User Manual

Page 64: 3 implementation, Ebv cyclone iv dbc4ce55 with nios, Configuration and resource consumption, Functionality, Implementation

Example Designs

III-52

Slave Controller

– IP Core for Altera FPGAs

6.2

EBV Cyclone IV DBC4CE55 with NIOS

6.2.1

Configuration and resource consumption

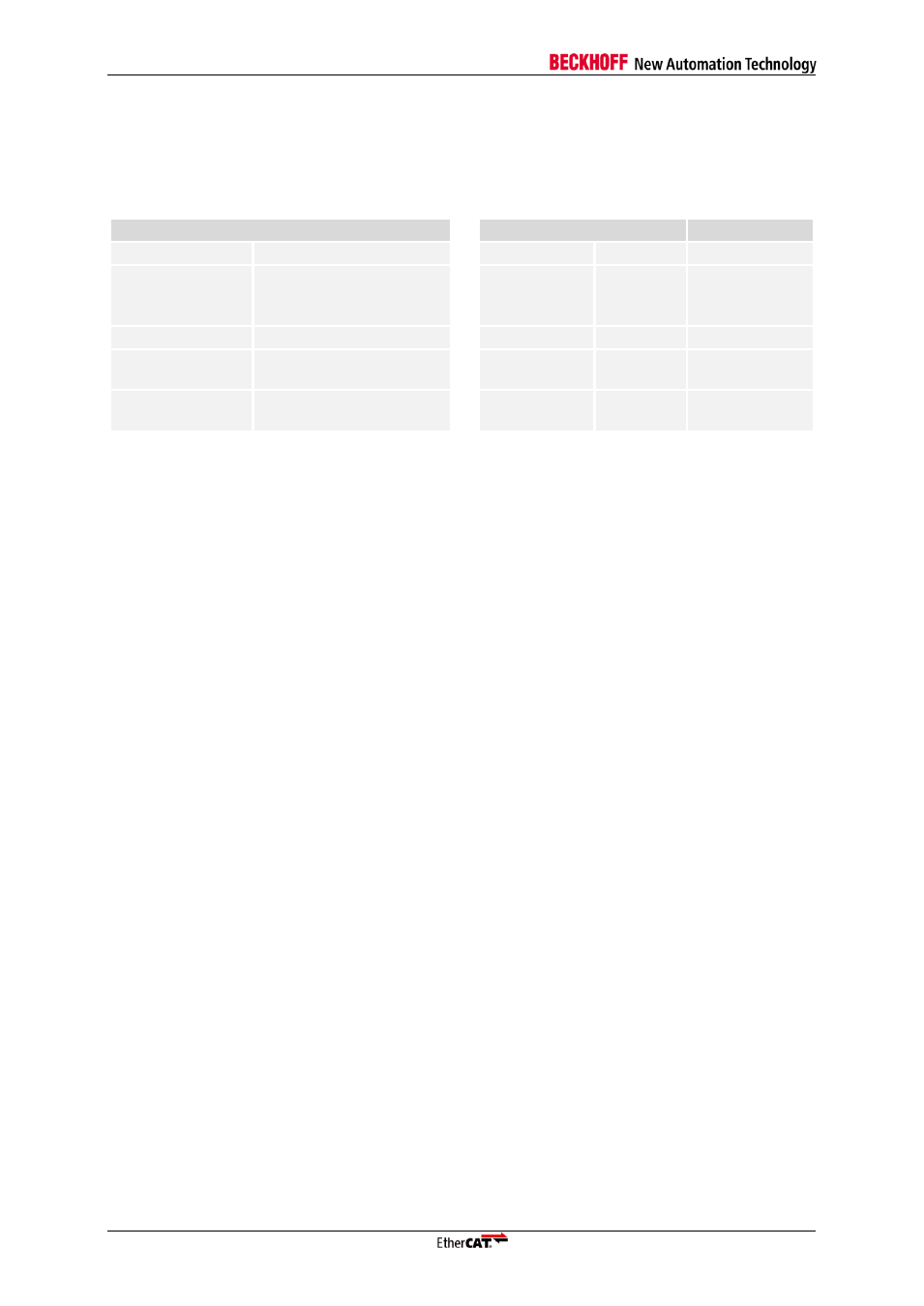

Table 14: Resource consumption NIOS example design DBC4CE55

Configuration

Resources

EP4CE55

Physical layer

2x RMII

Les

15,614

28 %

Internal Function

2x FMMU

4x SyncManager

1 KB RAM

Registers

7,476

13 %

Distributed clocks

none

M9K

136

52 %

Feature details

RUN_LED,

LED Test

PLLs

1

25 %

PDI

Digital I/O: 2 Byte IN, 2

Byte OUT

Multiplier

elements

0

0 %

NOTE: The board uses two individual PHY management interfaces, with both PHYs having the same PHY

addresses. Additionally, some of the PHY address bits have to be configured by extra logic inside the FPGA.

Because of the identical PHY addresses, the management interfaces on the board cannot be combined to one,

and thus, the EtherCAT IP Core cannot make use of the MII management interfaces of the PHY.

The Ethernet PHYs used on the DBC3C40 require Enhanced link detection for proper link loss reaction times.

Due to the hardware restrictions, it cannot be enabled on this board. This is suitable for evaluation purposes, but

not for production.

It is probably possible to change the PHY addresses on the board, combine the two management interfaces

inside the FPGA and add extra logic for proper configuration of the PHY address bits which are strapped on

signals connected to the FPGA. If this can be done, the PHY management interface as well as the Enhanced Link

Detection should be enabled.

6.2.2

Functionality

The NIOS demo application performs the following tasks:

Accept any EtherCAT Slave State request (copying AL Control to AL Status register)

Visualize EtherCAT Slave State (7-segment displays and running IO light in Operational mode).

The NIOS demo application is not suitable for production, it cannot be certified. Use the EtherCAT

Slave Stack Code (SSC, available from the ETG) for products.

6.2.3

Implementation

The SOPC needs to be generated before implementing the example design. Perform the following

steps for implementation:

1. Open Altera Quartus II

2. Open example design from

3. Choose Tools on the menu bar and select Qsys

…

4.

Open Qsys system “DBC4CE55_EtherCAT_NIOS_QSYS.qsys” and view IP configurations

5. Select Generate on the Generation tab to generate system

6.

Choose “Tools” on the menu bar and select “NIOS II Software Build Tools for Eclipse”

7. Select workspace, e.g. create

8. Choose File on the menu bar and select New

– “NIOS II Application and BSP from Template”

9. Select SOPC information file

“DBC4CE55_EtherCAT_NIOS_QSYS.sopcinfo”, project template

“BECKHOFF EtherCAT” and enter project name the “EtherCAT_Demo”

10. Select Finish

11. Choose Project on the menu bar and select

“Build all” to build the software project

“EtherCAT_Demo.elf” file is generated in the Debug-Folder of your workspace directory

12.

Select “Make Targets – Build…” from the context menu of the “EtherCAT_Demo” project.

13. Select

“mem_init_generate” and press “Build” button. This will generate the memory initialization

files.