4 avalon slave interface, 1 interface, Avalon slave interface – BECKHOFF EtherCAT IP Core for Altera FPGAs v3.0.10 User Manual

Page 125: Interface, Table 57: avalon signals, Figure 53: avalon signals

PDI Description

Slave Controller

– IP Core for Altera FPGAs

III-113

10.4 Avalon Slave Interface

10.4.1 Interface

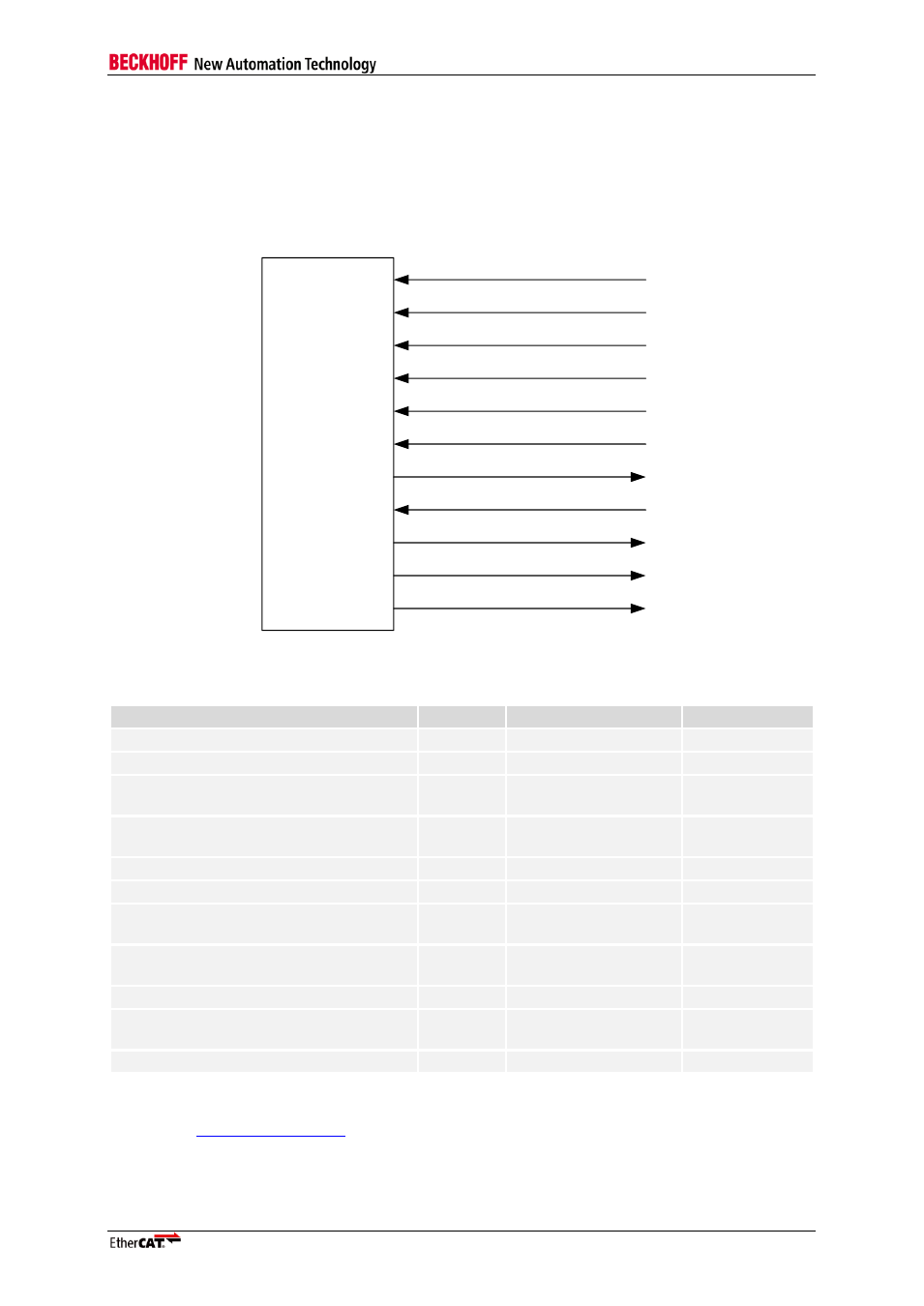

The Avalon Slave PDI is selected during the IP Core configuration. It uses memory

addressing/dynamic bus sizing. The signals of the Avalon interface are:

EtherCAT

IP core

CLK_PDI_EXT

PDI_AVALON_READ

PDI_AVALON_WRITE

PDI_AVALON_RD_DATA

PDI_AVALON_WR_DATA

PDI_AVALON_IRQ

PDI_AVALON_ADR

PDI_AVALON_BUSY

PDI_AVALON_CS

PDI_AVALON_SYNC0/1

PDI_AVALON_BE

Figure 53: Avalon signals

Table 57: Avalon signals

Signal

Direction

Description

Signal polarity

PDI_AVALON_CS

IN

Chip select

act. high

CLK_PDI_EXT

IN

Avalon Bus clock

PDI_AVALON_ADR

[18-ld(PDI_EXT_BUS_WIDTH):0]

IN

Address

PDI_AVALON_BE

[PDI_EXT_BUS_WIDTH/8-1:0]

IN

Byte enable

act. high

PDI_AVALON_READ

IN

Read request

act. high

PDI_AVALON_WRITE

IN

Write request

act. high

PDI_AVALON_RD_DATA

[PDI_EXT_BUS_WIDTH-1:0]

OUT

Read data

PDI_AVALON_WR_DATA

[PDI_EXT_BUS_WIDTH-1:0]

IN

Write data

PDI_AVALON_IRQ

OUT

Interrupt

act. high

PDI_AVALON_SYNC0/1

OUT

DC Sync0/1 used as

interrupts

act. high

PDI_AVALON_BUSY

OUT

Busy / Wait request

act. high

Please refer to the Avalon Memory-Mapped Interface Specification from Altera for details about the

Avalon bus

.