6 tested fpga/designflow combinations, Tested fpga/designflow combinations, Table 3: tested fpga/designflow combinations – BECKHOFF EtherCAT IP Core for Altera FPGAs v3.0.10 User Manual

Page 17

Overview

Slave Controller

– IP Core for Altera FPGAs

III-5

1.6

Tested FPGA/Designflow combinations

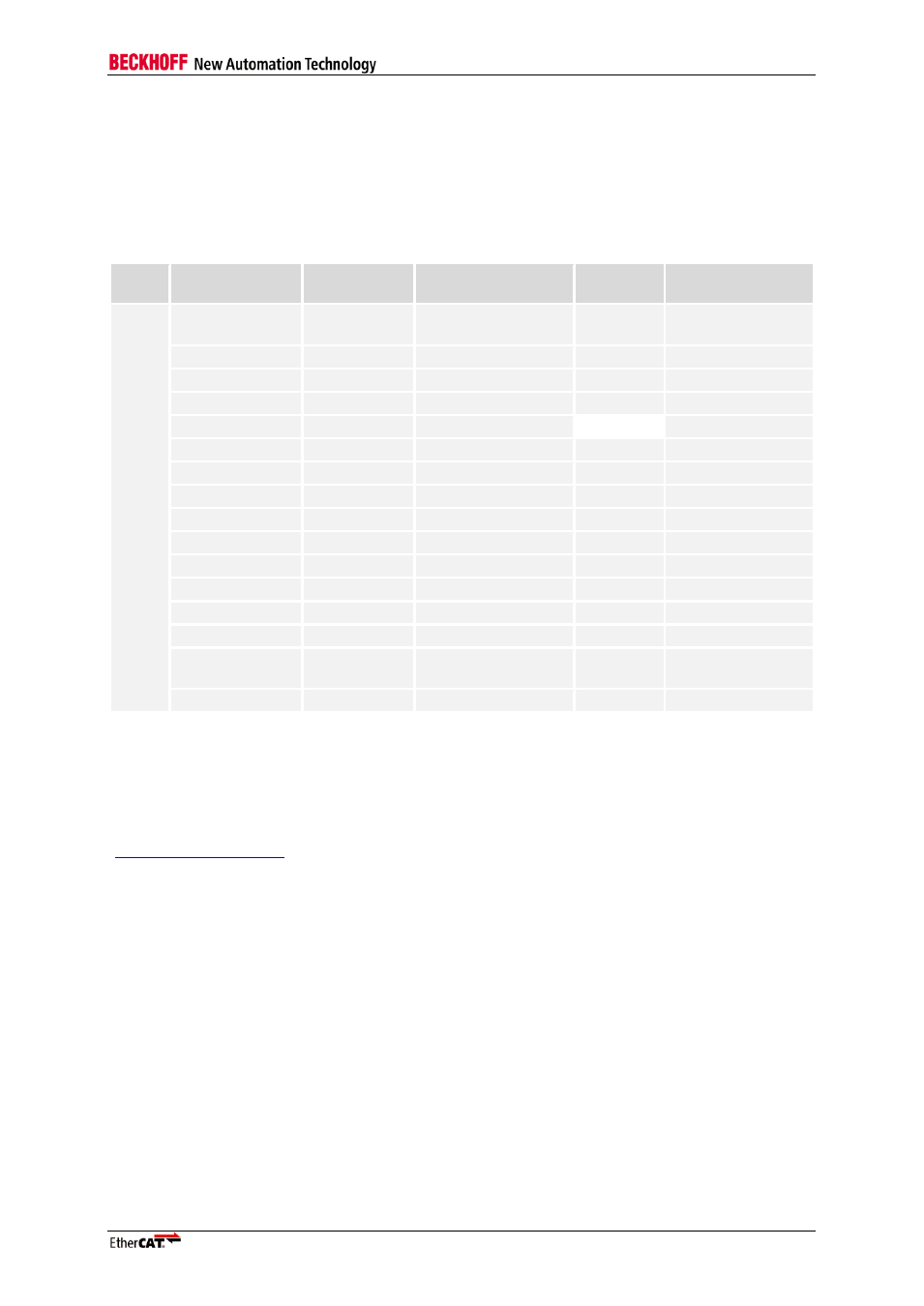

The EtherCAT IP Core has been synthesized successfully with different Quartus II versions and FPGA

families. Table 3 lists combinations of FPGA devices and design tools versions which have been

synthesized or even tested in real hardware. This list does not claim to be complete, it just illustrates

that the EtherCAT IP Core is designed to comply with a broad spectrum of FPGAs.

Table 3: Tested FPGA/Designflow combinations

IP

Core

Family

Device

Designflow

Test

Used Example

Designs

3.0.10

Cyclone III

EP3C40

Quartus II 13.1.4

Hardware

DBC3C40 Digital

I/O

Cyclone III LS

EP3CLS200

Quartus II 13.1.4

Synthesis

Cyclone IV E

EP4CE55

Quartus II 14.1

Hardware

DBC4CE55 Nios

Cyclone IV E

EP4CE115

Quartus II 14.1

Hardware

DE2-115 Nios

Cyclone V

5CEBA2

Quartus II 14.1

Synthesis

Cyclone V SoC

5CSEMA5

Quartus II 14.1

Synthesis

Stratix III

EP3SE50

Quartus II 13.1.4

Synthesis

Stratix IV E

EP4SE230

Quartus II 14.1

Synthesis

Stratix IV GT

EP4S40G

Quartus II 14.1

Synthesis

Stratix IV GX

EP4SGX70

Quartus II 14.1

Synthesis

Stratix V

5SGSMD4

Quartus II 14.1

Synthesis

Arria II GX

EP2AGX45

Quartus II 14.1

Synthesis

Arria V

5AGXMB3

Quartus II 14.1

Synthesis

Arria V GZ

5AGZME5

Quartus II 14.1

Synthesis

Intel Atom

E6x5C

EP2AGXE

6XXFPGA

Quartus II 13.1.4

Synthesis

MAX10

10M40DA

Quartus II 14.1

Synthesis

NOTE: Synthesis test means analysis, synthesis, fitter, and assembler. Hardware test means the design was

operational using real hardware.

NOTE: Turn on Analysis & Synthesis option: Auto RAM Replacement, otherwise the RAM inside the IP Core will

be implemented with individual registers.

Refer to the Hardware Data Sheet Section III Addendum available at the Beckhoff homepage

for latest updates regarding device support, design flow compatibility, and

known issues.