BECKHOFF EtherCAT IP Core for Altera FPGAs v3.0.10 User Manual

Page 35

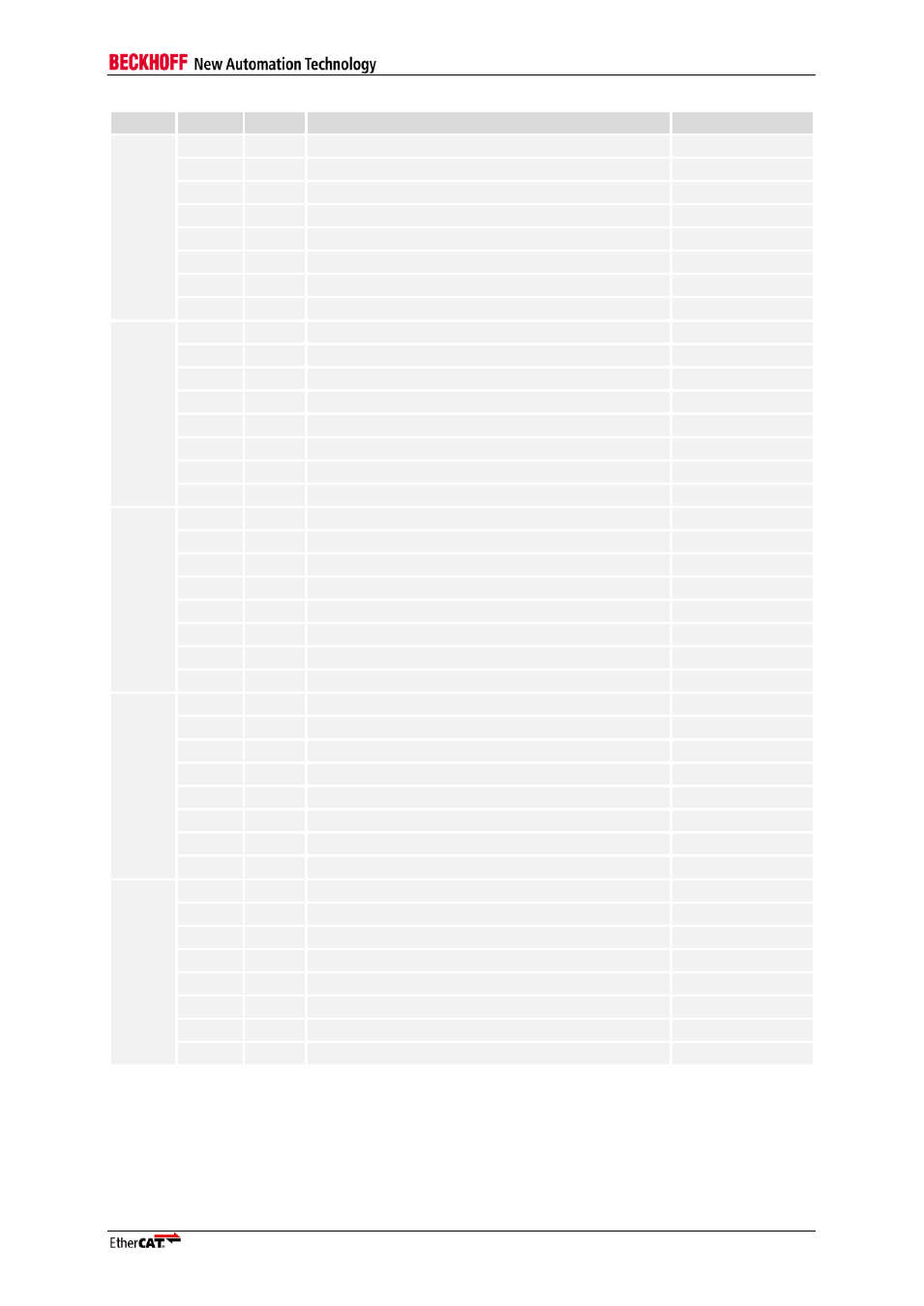

Features and Registers

Slave Controller

– IP Core for Altera FPGAs

III-23

Addr.

Bit

Feat.

Description

Reset Value

0F85

0

32

MI control by PDI possible

1

1

33

Automatic TX shift

c

2

34

EEPROM emulation by µController

c

3

35

Reserved

0

4

36

Reserved

0

5

37

Disable Digital I/O register (0x0F00:0x0F03)

c

6

38

Reserved

0

7

39

Reserved

0

0F86

0

40

Reserved

0

1

41

Reserved

0

2

42

RUN/ERR LED Override (0x0138:0x0139)

c

3

43

Reserved

0

4

44

Reserved

1

5

45

Reserved

0

6

46

Reserved

0

7

47

Reserved

0

0F87

0

48

Reserved

0

1

49

Reserved

0

2

50

Reserved

0

3

51

DC Sync1 disable

c

4

52

Reserved

0

5

53

Reserved

0

6

54

DC Receive Times (0x0900:0x090F)

c

7

55

DC System Time (0x0910:0x0936)

c

0F88

0

56

DC 64 bit

c

1

57

Reserved

0

2

58

PDI clears error counter

0

3

59

Avalon PDI

c

4

60

Reserved

0

5

61

PLB PDI

0

6

62

Reserved

0

7

63

Reserved

0

0F89

0

64

Reserved

0

1

65

Reserved

0

2

66

Reserved

0

3

67

Reserved

0

4

68

Reserved

0

5

69

Reserved

0

6

70

Reserved

0

7

71

Direct RESET

0